# Improved Interleaved Buck Converter with High-Step Down Conversion Ratio and Soft-Switching

Veera Venkata Subrahmanya Kumar Bhajana<sup>1</sup>, Pravat Biswal<sup>1</sup>, Pavel Drabek<sup>2</sup>, Vijay Kakani<sup>3</sup>

Cite this article as: WSK. Bhajana, P. Biswal, P. Drabek and V. Kakani, "Improved interleaved buck converter with high-step down conversion ratio and soft-switching," *Electrica*, 24(3), 767-779, 2024.

#### **ABSTRACT**

This article proposes a new interleaved buck converter with a high step-down conversion ratio and soft-switching. The soft-switching conditions for the main IGBTs are achieved with the aid of a simple auxiliary circuit, which comprises a resonant inductor, a resonant capacitor, and a diode. A new interleaved buck converter is realized by adopting two auxiliary circuits separately connected to each one of the legs to provide zero voltage switching (ZVS) and zero current switching (ZCS) turn-on operation. The major advantages of this converter are reduced switching losses, a high step-down ratio, reduced voltage stresses, and no limitation on duty ratio. To validate the theoretical analysis, a laboratory prototype of a 200 V–60 V converter system has been developed and achieved an efficiency of 96% at 250 W output power.

Index Terms—High step-down, interleaved buck converter, soft-switching, zero voltage switching (ZVS)

# I. INTRODUCTION

Buck converters find widespread application in scenarios requiring low output voltage and high output current, such as battery chargers, voltage regulator modules (VRMs) in the central processing units (CPUs) of computer systems, uninterruptible power supplies (UPSs), electric vehicles (EVs), and hybrid EVs [1-3]. In early days, a two-phase interleaved buck converter (TIBC) [4] incorporating a passive clamp circuit and coupled inductor was utilized. This implementation offered benefits such as reduced output current ripples, minimized voltage spikes, and an enhanced step-down ratio. Subsequently, improvements were made to TIBCs [5] by integrating a voltage-divider network and employing additional blocking capacitors to alleviate voltage stress on the main switching devices, thereby mitigating extreme short-duty cycles and achieving the desired voltage conversion ratio. Nevertheless, these enhancements also led to an increase in the number of switching devices and necessitated the incorporation of additional capacitors.

To increase overall efficiency, a buck converter with reduced output ripples and achieving soft-switching characteristics such as ZVS and zero current switching (ZCS) are the best solutions. In a Single Switch Buck Converter (SSBC) [6], ZVS turn-on operation to the main switch is achieved by utilizing the leakage inductance of a coupled inductor, an auxiliary switch, and a snubber capacitor. In addition to a coupled inductor in SSBC [7], an auxiliary passive circuit is used to achieve ZCS turn-on and ZVS turn-off characteristics. Similarly, ZCS turn-on and turn-off conditions are realized in another SSBC [8], which utilized the coupled inductor technique with three leakage inductances considered in addition to resonant elements.

Furthermore, the zero current transition (ZCT) condition is realized in a non-coupled inductor-based two-switch buck converter (TSBC) [9] by adopting an output inductor. In a two-channel buck converter (TCBC) [10] used for driving LEDs, a single series capacitor can be employed to balance the current across all channels, potentially simplifying the design by eliminating the need for separate control circuitry. However, this approach may be limited to applications with very low output power levels. To minimize the output ripples in a two-phase buck converter [11],

## **Corresponding author:**

Veera Venkata Subrahmanya Kumar Bhajana

## E-mail

bvvs.kumarfet|@kiit.ac.in, bvvskumar@ieee. org, kumarbvv@fel.zcu.cz

Received: June 4, 2024

**Revision Requested:** September 2, 2024 **Last Revision Received:** September 8, 2024

Accepted: September 26, 2024

Publication Date: October 23, 2024

DOI: 10.5152/electrica.2024.24063

Content of this journal is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License.

<sup>&</sup>lt;sup>1</sup>School of Electronics Engineering, KIIT University, Bhubaneswar, India

<sup>&</sup>lt;sup>2</sup>Regional Innovation Centre for Electrical Engineering, University of West Bohemia in Pilsen, Plzeň, Czech Republic

<sup>&</sup>lt;sup>3</sup>Department of Integrated System Engineering, Inha University, Incheon, South Korea

series connections of coupled inductors provide a viable solution, and in addition to that, a lossless snubber is included to obtain the ZCS turn-on condition. In a TSBC [12, 13], additional input inductors and switched-capacitor cells are utilized to obtain the desired high step-down ratio. To develop ripple-free high-power applications, interleaved buck converters [14-16] are preferable with a simple series capacitor in addition to a coupled inductor, and those converters are further improved with a valley-fill capacitor cell (VFCC) [17] by replacing series capacitors to ensure desired conversion ratios.

In this paper, a novel interleaved buck converter is realized with soft switching and a high step-down conversion ratio. To ensure soft switching operation of the main switches, two auxiliary circuits are adopted to a conventional buck converter. To provide the desired conversion ratio, a series capacitor is used in the power flow path. The proposed converter offers the following advantages:

- · No auxiliary switches are used.

- ZVS turn-on for the main switch S<sub>1</sub>.

- ZCS turn-on for the main switch S<sub>2</sub>.

- · Fewer additional devices.

- The voltage across switching devices is less than the input voltage.

# **II. DESCRIPTION AND OPERATING MODES**

# A. Description of Proposed Interleaved Buck Converter

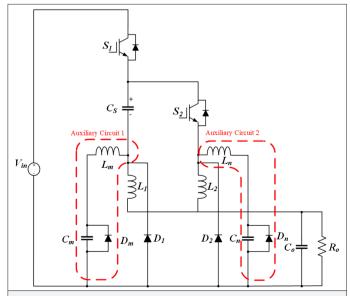

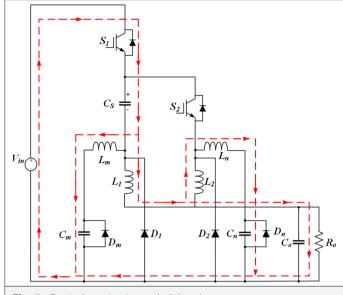

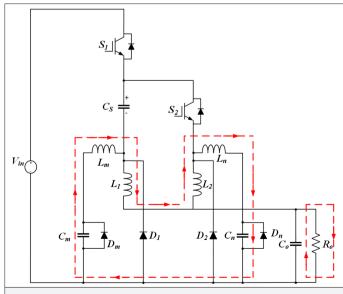

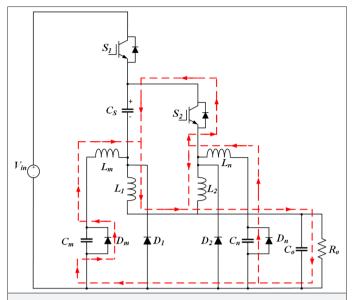

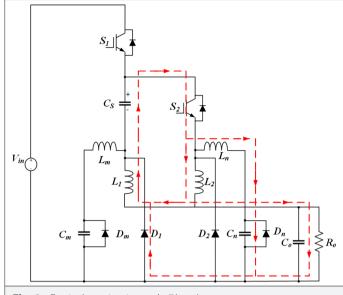

An improved soft-switching interleaved buck converter, shown in Fig. 1, consists of two main switching devices  $(S_1, S_2)$  connected in series, a coupling capacitor  $(C_s)$  is placed in the power flow path, and two output inductors  $(L_1, L_2)$ . In order to provide zero voltage switching (ZVS) turn-on condition to switch  $S_1$ , and zero current switching (ZCS) turn-on condition to switch  $S_2$ , the resonant network  $S_1$ , and another resonant network  $S_2$ , and  $S_3$  is connected to the leg of  $S_3$ .

The major merits of this topology are:

**Fig. 1.** Proposed schematic of interleaved buck converter with high step-down conversion ratio

- Voltage stresses of the main IGBTs are half of the input voltage.

- Reduced switching losses.

- · Lower output current ripple.

- · Lower conversion ratio.

- · Soft-switching conditions: ZVS and ZCS.

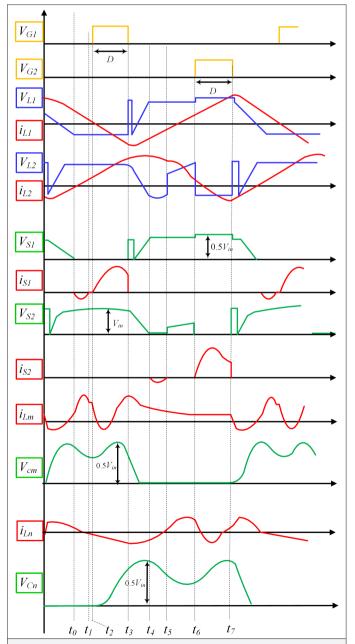

Fig. 2 shows the PWM signals  $V_{\rm G1}$  and  $V_{\rm G2}$  for switches  $S_{\rm 1}$ , and  $S_{\rm 2}$  respectively, with duty cycle (*D*) intervals  $t_2$ – $t_3$  and  $t_6$ – $t_7$ , representing the controlled switching actions in the interleaved buck converter. A minimal duty ratio (D) of 20% has been chosen for both  $S_{\rm 1}$  and  $S_{\rm 2}$  to ensure the desired conversion ratio. The operation of this converter is divided into seven modes, denoted as  $t_0$ – $t_7$ , as illustrated by the key waveforms in Fig. 2 and corresponding equivalent circuits for all the modes are shown in Figs. 3-9.

**Fig. 2.** Key waveforms. (Note that the waveforms are represented from the obtained simulation results.)

# **B.** Operating Modes

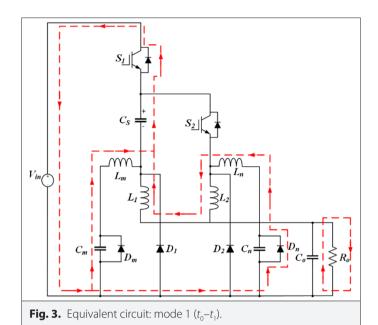

Mode 1  $(t_0-t_1)$ : At  $t_0$  body diode of IGBT,  $S_1$  is begins conducting to provide the path of resonant tank current. Therefore, it fulfills the ZVS turn-on condition. At the end of this interval, the S<sub>1</sub> body diode stops conducting. The governing equations of  $i_{S1}$ ,  $V_{Cm'}$ ,  $i_{L1'}$ , and  $i_{ln}$  are expressed in:

$$i_{S1}(t) = 0 \tag{1}$$

$$V_{Cm}(t) = V_{Cm}(t_0) + V_{Cm}(t_0)(1 - \cos \omega_1(t - t_0))$$

(2)

where

$$\omega_1 = \frac{1}{\sqrt{(L_n + L_2 + L_1 + L_m)\left(\frac{C_m \times C_n}{C_m + C_n}\right)}}$$

$$i_{Ln}(t) = i_{Ln}(t_0) + (V_{Cn}(t_0) - V_0) \sqrt{\frac{C_n}{L_n + L_2}} \times \sin \omega_2(t - t_0)$$

(3)

**Fig. 4.** Equivalent circuit: mode 2  $(t_1-t_2)$ .

**Fig. 5.** Equivalent circuit: mode 3  $(t_2-t_3)$ .

where

$$\omega_2 = \frac{1}{\sqrt{(L_n + L_2)C_n}}$$

$$i_m(t) = i_{Ln}(t) - I_0$$

(4)

$$V_{Cn}(t) = V_n(t_0)\cos\omega_2(t - t_0)$$

(5)

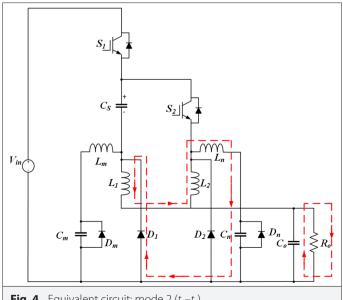

Mode 2 ( $t_1$ – $t_2$ ): During this mode, IGBT,  $S_1$  current reaches zero and  $C_m$ discharges to  $V_{in}$ .

Mode 3  $(t_2-t_3)$ : At  $t_2$   $S_1$  is turned on with zero voltage and zero current switching (ZVZCS) condition. Throughout this mode, the output power flows via  $V_{in}$  –  $S_1$  –  $L_1$ . The governing equations for  $i_{Lm'}$   $i_{L1'}$   $i_{L2'}$   $V_{Cm'}$ and  $V_{Cn}$ .

$$i_{51}(t) = V_{in} \sqrt{\frac{C_{eq}}{L_m}} \operatorname{Sin}\omega_3(t - t_2)$$

(6)

**Fig. 6.** Equivalent circuit: mode 4  $(t_3-t_4)$ .

**Fig. 7.** Equivalent circuit: mode 5  $(t_4-t_5)$ .

where

$$C_{eq} = \frac{C_s \times C_m}{C_s + C_m}$$

and  $\omega_3 = \frac{1}{\sqrt{L_m C_{eq}}}$

$$V_{cm}(t) = V_{cm}(t_2) + V_{cm}(t_2) \left[ 1 - \cos \omega_4(t - t_2) \right]$$

(7)

where

$$\omega_4 = \frac{1}{\sqrt{L_m C_m}}$$

$$i_{L1}(t) = i_L(t_2) + \frac{1}{I_s} [V_{in} - V_{Cs} - V_o](t - t_2)$$

(8)

$$i_{Ln}(t) = i_{L1}(t_2) - I_0 \sin \omega_5(t - t_2)$$

(9)

where

$$\omega_5 = \frac{1}{\sqrt{L_{eq}C_n}}$$

and  $L_{eq} = L_1 + L_2 + L_n$

Mode 4  $(t_3-t_4)$ : During this mode, the voltage across IGBT  $S_1$  linearly increases and  $S_2$  falls to zero at the end of this interval.  $C_n$  is charged

**Fig. 9.** Equivalent circuit: mode  $7(t_6-t_7)$ .

to 0.5 $V_{\rm in}$  at  $t_4$  and  $C_m$  is completely discharged to zero. The expressions for  $i_{Lm'}$   $i_{L1'}$   $i_{L2'}$   $V_{Cm'}$  and  $V_{Cn}$  are as follows:

$$i_{52}(t) = \left(V_{Cs}\sqrt{\frac{C_{eq1}}{L_n}}\right) \sin \omega_6(t - t_3)$$

(10)

where

$$\omega_6 = \frac{1}{\sqrt{L_n C_{eq1}}}$$

;  $C_{eq1} = \frac{C_S \times C_n}{C_S + C_n}$

$$V_{cn}(t) = V_n(t_3) + i_{52}(t) \sqrt{\frac{L_n}{C_{eq1}}} \sin \omega_6(t - t_3)$$

(11)

$$i_{L2}(t) = i_{L2}(t_3) + V_{Cs} \sqrt{\frac{C_s}{L_2 + L_1}} \sin \omega_7(t - t_3)$$

(12)

where

$$\omega_7 = \frac{1}{\sqrt{(L_2 + L_1)C_s}}$$

Mode 5  $(t_4-t_5)$ : Throughout this mode, the body diode of  $S_2$  is in a conducting state and  $L_n$ ,  $C_n$  are in a resonating state. The governing equations for  $i_{Ln'}$ ,  $i_{L1'}$ ,  $i_{L2'}$ ,  $V_{Cn'}$  and  $V_{Cn}$  are expressed in:

$$i_{S1}(t) = 0$$

(13)

$$i_{Lm}(t) = i_{Lm}(t_4) + \left(\frac{V_o}{L_1 + L_m}\right)(t - t_4)$$

(14)

$$i_{L2}(t) = \left(\frac{V_{Cn}(t_4) - V_o}{L_n + L_2}\right)(t - t_4)$$

(15)

where

$$\omega_8 = \frac{1}{\sqrt{(L_n + L_1)C_s}}$$

$$i_{S1}(t) = (V_{Cn}(t_4) - V_{Cs} - V_o)\sqrt{\frac{C_s}{L_n + L_1}} \sin \omega_8(t - t_4)$$

(16)

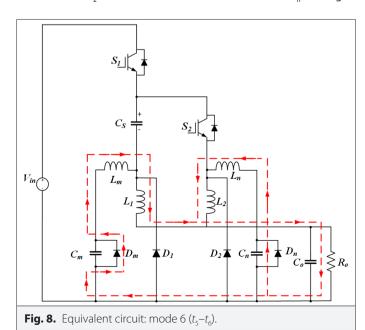

Mode 6  $(t_s-t_6)$ : During this mode, the voltage across IGBT,  $S_2$  reaches  $V_o$  and still  $L_{n'}$ ,  $C_n$  are in a resonating condition. The corresponding equations for  $i_{S1}$ ,  $i_{Ln'}$ ,  $i_{L1}$ ,  $i_{L2}$ ,  $V_{Cn'}$  and  $V_{Cn}$  are expressed as follows:

$$i_{s1}(t) = 0$$

(17)

$$V_{Cm}(t) = 0 ag{18}$$

$$i_{Lm}(t) = i_{Lm}(t_5)$$

(19)

$$V_{cn}(t) = V_{in}(t_5) + i_{s2}(t) \sqrt{\frac{L_n}{C_{eq1}}} \sin \omega_6(t - t_5)$$

(20)

$$i_{Ln}(t) = i_{S2}(t) - i_{L2}(t)$$

(21)

Mode 7 ( $t_6$ – $t_7$ ): At  $t_6$ , IGBT  $S_2$  is turned on with zero current switching (ZCS), and output power flows via  $V_{in}$ – $S_2$ – $L_2$ .

$$i_{s2}(t) = V_{Cs} \sqrt{\frac{C_{eq1}}{L_n}} \sin \omega_6(t - t_6)$$

(22)

$$V_{cn}(t) = V_{in}(t_6) + i_{52}(t) \sqrt{\frac{L_n}{C_{eq1}}} \sin \omega_6(t - t_6)$$

(23)

$$i_{lm}(t) = i_{52}(t) - i_{12}(t) \tag{24}$$

$$i_{L2}(t) = i_{L2}(t_6) + V_{Cs} \sqrt{\frac{C_s}{L_2 + L_1}} \sin \omega_9(t - t_6)$$

(25)

where  $\omega_9 = \frac{1}{\sqrt{(L_1 + L_2)C_s}}$

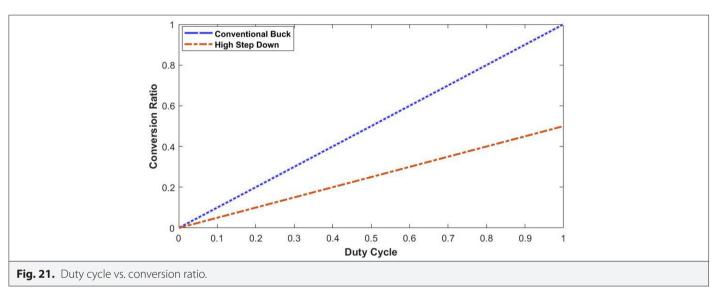

# III. DC CONVERSION RATIO

The conversion ratio of this converter is determined through the utilization of the voltage–second balance (V-S-B) equation on  $L_1$  and  $L_2$ . Typically, the conversion ratio is calculated by examining two operational conditions: the first condition when IGBT  $S_1$  is ON state and the second condition when the IGBT,  $S_1$  is in the OFF state.

Apply V-S-conB on  $L_{1,}$  when  $S_{1}$  is turned-on,  $L_{1}$  voltage can be written as:

$$V_{L1} = V_{in} - V_{Cs} - V_0 (26)$$

When S is turned off, then  $L_1$  voltage can be expressed as:

$$V_{l1} = -V_0 (27)$$

Apply V-S-B on  $L_1$  when  $S_2$  is turned-on,  $L_1$  voltage can be written as:

$$V_{L2} = V_{Cs} - V_0 (28)$$

When  $S_2$  is turned off, then  $L_1$  voltage can be expressed as:

$$V_{L2} = -V_0 (29)$$

Applying Volt–second balance for the inductor,  $L_1$ ,

$$(V_{in} - V_{Cs} - V_0)D + (-V_0)(1 - D) = 0$$

(30)

$$(V_{in} - V_{Cs})D = V_0D + (V_0)(1-D)$$

(31)

$$\left(V_{in} - V_{Cs}\right)D = V_0 \tag{32}$$

Applying Volt–second balance for the inductor,  $L_{\gamma}$ ,

$$(V_{Cs} - V_0)D + (-V_0)(1-D) = 0 (33)$$

$$V_{C_5}D = V_0 \tag{34}$$

$$V_{Cs} = \frac{V_0}{D} \tag{35}$$

The voltage of the coupling capacitor  $C_s$  can be obtained by (28) and (29), which equals to half of the input voltage. The voltage conversion ratio of the converter is given by:

$$\left(V_{in} - \frac{V_0}{D}\right)D = V_0 \tag{36}$$

$$V_{in}D = 2V_0 \tag{37}$$

$$\frac{V_0}{V_{in}} = \frac{D}{2} \tag{38}$$

# **IV. DESIGN ANALYSIS**

The criteria for achieving soft-switching conditions ZVS/ZCS during the turn-on of the switches  $S_1$  and  $S_2$  are established through the inequality defined in (39). Increasing the value of characteristic impedance (Z) helps in reducing the peak currents across the switching devices. Maintaining the parameter  $I_z$  at minimal levels is necessary to ensure the ZVS and ZCS turn-on conditions.

$$I_7 \ge I_0 \tag{39}$$

$$I_Z = \frac{V_{in}}{\sqrt{\frac{L_{m,n}}{C_{m,n}}}} \tag{40}$$

The resonant inductors  $L_{\rm m}$ ,  $L_{\rm n}$  and capacitors,  $C_{\rm m}$ ,  $C_{\rm n}$  are constrained by the resonant frequency:

$$f_r = \frac{\omega}{2\pi} = \frac{1}{2\pi\sqrt{L_{m,n}C_{m,n}}} \tag{41}$$

The following variables are defined:

Characteristic impedance,

$$Z = \sqrt{\frac{L_{m \approx n}}{C_{m \approx n}}} \tag{42}$$

Resonant angular frequency,

$$\omega = \frac{1}{\sqrt{L_{m \approx n} C_{m \approx n}}} \tag{43}$$

Resonant capacitors  $C_{m}$ ,  $C_{n}$  are selected by the following relation:

$$C_{m \approx n} \le \frac{1}{\omega} \left( \frac{I_o}{V_{in}} \right) \left( \frac{1}{2f_s} \right) \tag{44}$$

Resonant inductors  $L_{mr}$ ,  $L_{n}$  are selected by the following relation:

$$L_{m \approx n} = \frac{1}{C_{m \approx n} (2\pi f_t)^2} \tag{45}$$

Normalized frequency is defined by,

$$f_n = \frac{f_r}{f_c} \tag{46}$$

The selection of switches  $S_1$ ,  $S_2$  depends on peak voltage stress and current stresses:

$$V_{\rm S1} = \frac{V_{\rm in}}{2} \tag{47}$$

$$V_{\rm S2} = V_{in} \tag{48}$$

$$I_{51,52} = I_z + I_o (49)$$

The selection of diodes  $D_{m}$ ,  $D_{n}$  depends on current stress:

$$I_{Dm\approx n} = I_o \tag{50}$$

The voltages across the capacitor  $C_{ny}$ ,  $C_n$  are defined by:

$$V_{Cm\approx n} = 2V_{in} \tag{51}$$

The selection of IGBTs and diodes in the converter is made based on (47), (48), and (49). The maximum current stresses of the IGBTs and diodes are 10A, and voltage across the IGBT is equals to the input voltage. The maximum value of resonant capacitors  $C_{\rm m}$ ,  $C_{\rm n}$  can be used below 40 nF, and resonant inductors can be selected at 30  $\mu$ H from (44) and (45), respectively.

# V. LOSS DISTRIBUTION OF THE PROPOSED CONVERTER

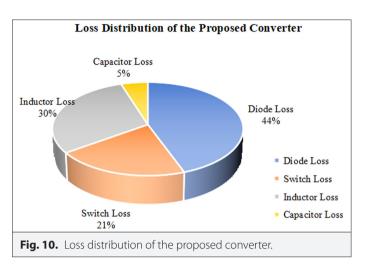

This section presents the loss distribution of the proposed converter while operating at 250 W output power with 200 V input voltage and 60 V output voltage; output current: 4.16 A.

# A. Switch Losses

The RMS current of the switch is calculated by:

$$i_{sw(rms)} = I_o + V_{cm} \times \sqrt{\frac{C_m}{L_m}}$$

(52)

Power loss in the switch

$$P_{sw} = i_{sw(rms)}^{2} \times r_{(on)} + \frac{V_{sw} \times i_{sw} \times f_{sw}(t_r + t_f)}{6}$$

(53)

where  $r_{l}$  on-state resistance

#### **B. Inductor Losses**

The RMS current in the inductor  $(i_{L1(rms)})$  is calculated by:

$$i_{L1(rms)} = I_o \sqrt{D \left( 1 + \frac{\Delta i_L}{i_{Lmin}} \left( 1 + \frac{1}{3} \times \frac{\Delta i_L}{i_{Lmin}} \right) \right)}$$

(54)

where  $\Delta i_{\scriptscriptstyle L} = {\rm input}$  ripple;  $i_{\scriptscriptstyle Lmin} = {\rm minimum}$  input current;  $I_{\scriptscriptstyle o} = {\rm output}$  current

Power loss of the inductors

$$P_{Lloss(rms)} = I_{L(rms)}^{2} \times r_{L}$$

(55)

where  $r_i$  = inductor internal resistance

# C. Diode Losses

The diodes  $D_{1r}$   $D_{2}$  rms average currents  $(I_{D1(rms)},I_{D1(avg)})$  and total power loss  $(P_{loss(rms)})$  are given by

$$I_{D1(rms)} = \frac{V_{cs} - V_o}{2\pi} \sqrt{\frac{C_s}{L_2}} \sqrt{\frac{D}{3}}$$

(56)

where

$$V_{cs} = \frac{V_{in}}{2}$$

$$I_{D1(avg)} = \frac{V_{cs} - V_o}{2\pi} \times \sqrt{\frac{C_s}{L_2}} \times D \tag{57}$$

$$P_{loss(rms)} = I_{d(rms)}^{2} \times r_{d} + V_{\gamma} \times I_{d(avq)}$$

(58)

where  $V\gamma$  = forward voltage drop.

The diodes  $D_{m}$ ,  $D_{n}$  rms and average currents ( $I_{Dm(rms)}$ ,  $I_{Dm(avg)}$ ) are given by:

$$I_{Dm(avg)} = \frac{V_{cs} - V_o}{2\pi} \sqrt{\frac{C_S}{L_m + L_2}} \times D$$

(59)

$$I_{Dm(rms)} = \frac{V_{cs} - V_o}{2\pi} \sqrt{\frac{C_s}{L_m + L_2}} \times \sqrt{\frac{D}{3}}$$

(60)

$$P_{Dloss} = I_{d(rms)}^{2} \times r_{d} + V_{\gamma} \times I_{d(avg)}$$

$$(61)$$

It can be seen from Table I, by using equations (52–61), that the losses in the diodes are 4.28 W, the losses in inductors are 2.88 W, and the losses

TABLE I. OVERALL LOSSES OF THE PROPOSED CONVERTER

| Device Type                   | Components                                                        | $r_{\scriptscriptstyle (on)}\left( m\Omega  ight)$ | $V_{max}(V)$ | <i>V</i> γ (V) | $I_{avg}\left(A\right)$ | I <sub>max</sub> (A) | Loss (W) | Loss Percentage |

|-------------------------------|-------------------------------------------------------------------|----------------------------------------------------|--------------|----------------|-------------------------|----------------------|----------|-----------------|

| Diode                         | $D_{m'}, D_{n'}, D_1, D_2$                                        | 2                                                  | 250          | 0.8            | 1.9                     | 6.3                  | 4.28     | 44.31           |

| Switch                        | S <sub>1</sub> , S <sub>2</sub>                                   | 33                                                 | 240          | -              | 4.6                     | 7.8                  | 2.02     | 20.91           |

| Inductor                      | L <sub>a</sub> , L <sub>b</sub> , L <sub>m</sub> , L <sub>n</sub> | 60                                                 |              | -              | 0.81                    | 2.29                 | 2.88     | 29.81           |

| Capacitor                     | $\subset_{a'}\subset_{b'}\subset_o$                               | 1000                                               | 250          | -              | -                       | 0.14, 0.14, 1.01     | 0.484    | 4.97            |

| Total losses in the converter |                                                                   |                                                    |              |                |                         |                      | 9.664    | 100.00          |

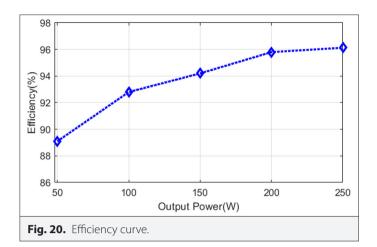

in capacitors are 0.484 W. The switching losses are reduced as soft-switching is implemented to turn on the switches, which is 2.02 W. The overall losses are 9.664 W, while the converter operates at 250 W output power, obtaining an overall efficiency of the converter of 96.13%. The loss distribution of the proposed converter is shown in Fig. 10.

#### VI. SIMULATION RESULTS

The converter is designed using the PLECS simulation tool. The proposed converter is simulated with the following parameters:

Input voltage: 200 V

Output voltage: 60 V

Output resistance: 50 Ω

Switching frequency: 40 kHz

Output power: 250 W

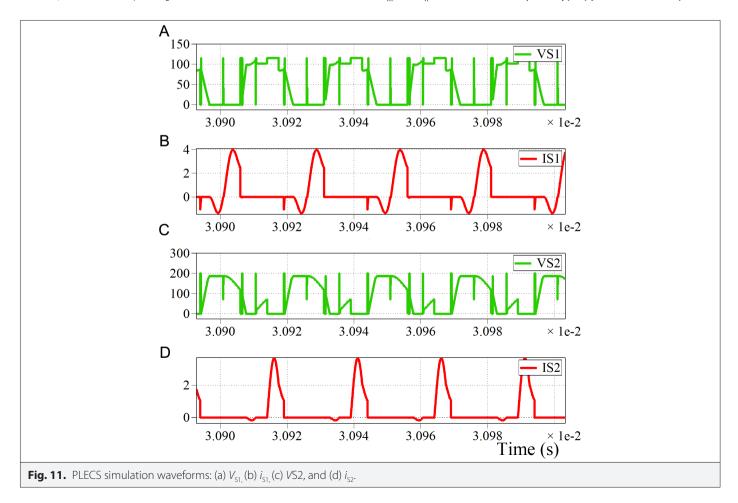

Fig. 11 shows the voltage and current waveforms of the main IGBTs  $S_1$  and  $S_2$ . It can be seen from the obtained results that the voltage stress of  $S_1$  is equal to half of the input voltage, and  $S_2$  is also less than the input voltage. The resonant networks are employed for both legs separately. These help in providing ZVZCS and ZCS condition turnon for  $S_1$  and  $S_2$  switching devices, respectively.

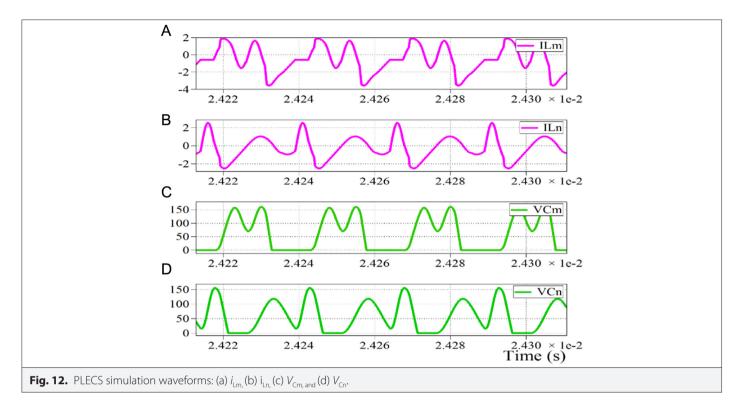

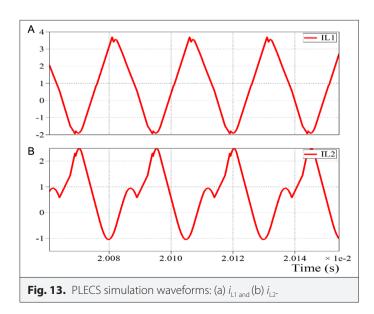

Fig. 12 shows the voltages of  $C_{\rm m'}$ ,  $C_{\rm n'}$ , and current waveforms  $L_{\rm m'}$ ,  $L_{\rm n}$ . Current through the inductor equals the output current, and voltage across  $C_{\rm m'}$ ,  $C_{\rm n}$  is 160 V, each. Fig. 13 depicts the current waveforms of the output inductors  $L_{\rm 1}$  and  $L_{\rm 2}$ .

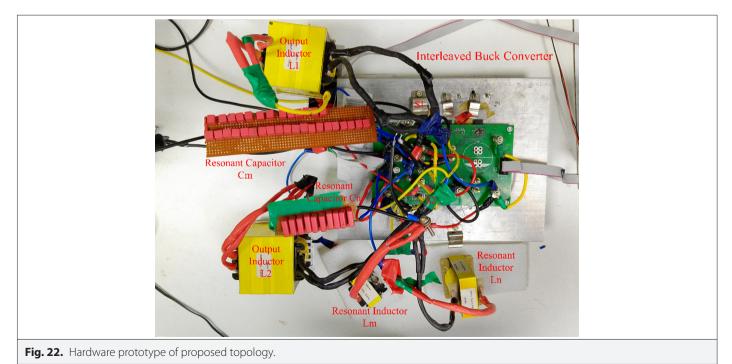

#### **VII. EXPERIMENTAL RESULTS**

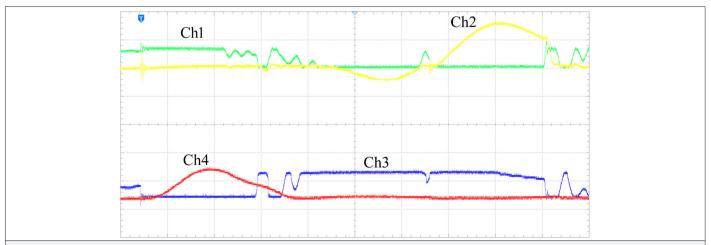

To validate the theoretical analysis, a laboratory prototype of the proposed 200V-60V-250W converter system was implemented. The experimental setup's parameters and components are detailed in Table II. Experimental verifications were performed under open-loop conditions, and PWM signals were generated using a TMSF28335 docking station. Two SKYPER 32R drivers were used to generate the desired 40 kHz switching frequency. Ferrite E-cores were utilized for inductors,  $L_1$  and  $L_2$ , each with 100  $\mu$ H, along with resonant inductors  $L_m$  and each with 30  $\mu$ H. Polypropylene (PP) film capacitors,

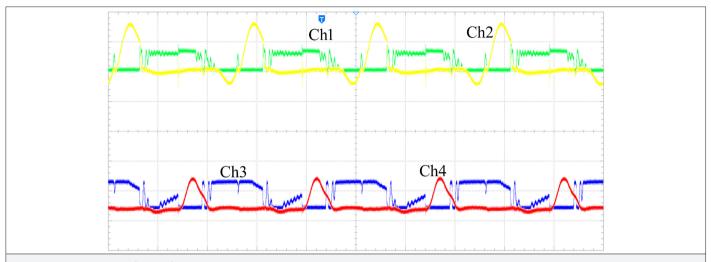

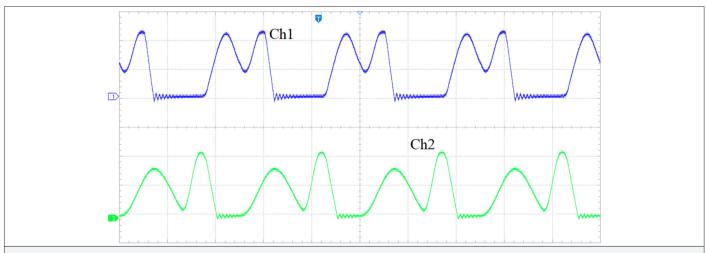

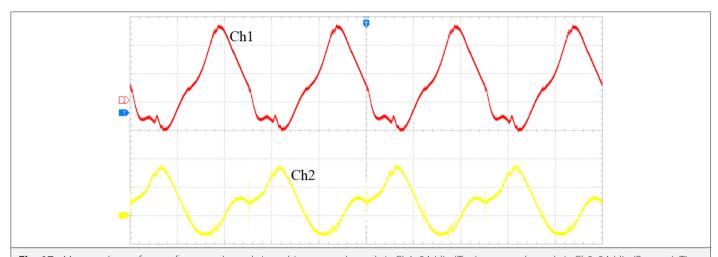

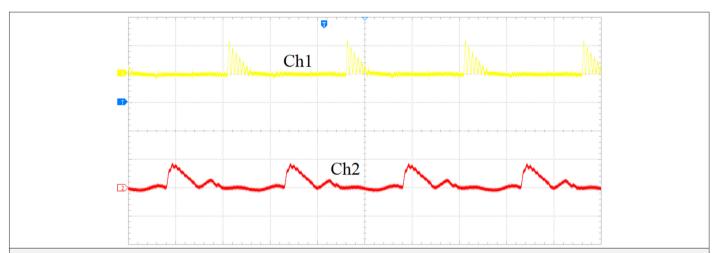

specifically WIMA FKP1R013304C, were employed for resonant capacitors  $C_{\rm m}$  and  $C_{\rm n}$ , with a total capacitance of 40 nF achieved by connecting 12 numbers of 3300 pF capacitors in parallel. WOLFSPEED SiC SCHOTTKY diodes C6D06065A were used as  $D_{\rm m}$  and  $D_{\rm n}$ , while Infineon IGBTs IHW25N120R2 served as  $S_1$  and  $S_2$ . The PWM signals had a 20% duty cycle during measurements. The converter was tested with a 200 V input voltage, yielding a 60 V output voltage with a 20% duty cycle and a load resistance ( $R_0$ ) of 40  $\Omega$ . Waveforms of the main switching devices  $S_1$  and  $S_2$  are presented in Fig. 14, indicating a voltage of 100 V across  $S_1$  and 200 V across  $S_2$ , with peak currents of 7A and 5A, respectively. Both switches exhibited zero voltage and zero current turn-on conditions without additional losses. Fig. 15 shows waveforms of  $L_{\rm m}$  and  $L_{\rm n}$ , with an average current of 5A.

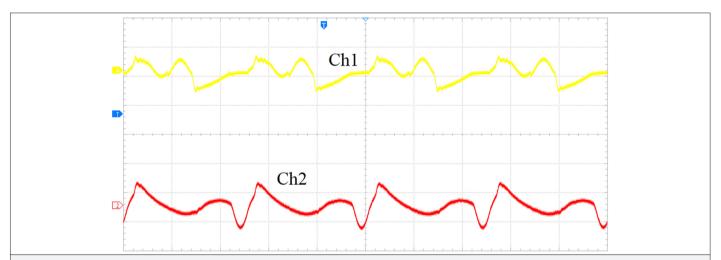

Fig. 16 illustrates the voltage across resonant capacitors  $C_{\rm m}$  and  $C_{\rm n}$ , showing a maximum voltage of approximately 200 V for each capacitor. Figs. 17 and 18 depict the current through inductors  $L_1$ ,  $L_2$ , and diodes  $D_{\rm m}$ ,  $D_{\rm n}$ , respectively, with peak currents matching the output current. Fig. 19 shows the turn-on and turn-off transitions of  $S_1$  and  $S_2$  at a maximum output power of 250 W. Fig. 20 shows a plotted curve between efficiency versus output power. It can be seen that the lower efficiency obtained at 150 W output power is 93%, and at 250 W output power, 96.2% is the maximum efficiency. Voltage conversion ratios are plotted in Fig. 21 between two topologies: one is conventional interleaved buck converter and the other one is extended interleaved buck converter. Fig. 22 shows the hardware prototype developed for the proposed interleaved buck DC-DC converter. Table III illustrates the comparison of existing topologies with the proposed converter. A higher number of auxiliary switches are

| TABLE II. PROTOTYPE PAR | RAMETERS  Symbol Value          |           |  |  |  |  |  |

|-------------------------|---------------------------------|-----------|--|--|--|--|--|

| Parameter               | Symbol                          | Value     |  |  |  |  |  |

| Input voltage           | $V_{in}$                        | 200 V     |  |  |  |  |  |

| Output power            | Po                              | 250 W     |  |  |  |  |  |

| Switching frequency     | f <sub>sw</sub>                 | 40 kHz    |  |  |  |  |  |

| Resonant inductors      | $L_{m'}L_n$                     | 30 μΗ     |  |  |  |  |  |

| Resonant capacitors     | $C_{m'}C_n$                     | 40 nF     |  |  |  |  |  |

| Inductors               | $L_{1,}L_{2}$                   | 100 μΗ    |  |  |  |  |  |

| Output capacitor        | Co                              | 470 μF    |  |  |  |  |  |

| IGBTs                   | S <sub>1</sub> , S <sub>2</sub> | IHW25N120 |  |  |  |  |  |

| Diodes                  | $D_1, D_2, D_m, D_n$            | C6D06065A |  |  |  |  |  |

**Fig. 14.** Measured waveforms of  $V_{S1}$ ,  $V_{S2}$ ,  $i_{S1}$ ,  $i_{S2}$  collector-emitter voltage  $V_{S1}$ , Ch1: 250V/div (Top); collector current  $i_{S1}$ , Ch2: 5A/div (Top). Collector-emitter voltage  $V_{S2}$ , Ch3: 250V/div (Bottom). Collector current  $i_{S2}$ , Ch4: 5A/div (Bottom). Time scale: 10  $\mu$ s/div.

**Fig. 15.** Measured waveforms of current through  $L_m$  and  $L_n$  Current through  $L_m$  Ch1: 5A/div (Top); Current through  $L_n$  Ch2: 5A/div (Bottom). Time scale: 10  $\mu$ s/div.

**Fig. 16.** Measured waveforms of  $V_{Cm}$  and  $V_{Cn}$  Voltage across  $C_m$  Ch1: 100V/div (Top); Voltage across  $C_n$  Ch2: 100V/div (Bottom). Time scale: 10  $\mu$ s/Div.

**Fig. 17.** Measured waveforms of current through  $L_1$  and  $L_2$  current through  $L_1$  Ch1: 2A/div (Top); current through  $L_2$  Ch2: 2A/div (Bottom). Time scale: 10  $\mu$ s/div.

**Fig. 18.** Measured waveforms currents through diodes  $D_m$  and  $D_n$ . Currents through diodes  $D_m$  Ch1: 5A/div (Top); Current through diode  $D_n$  Ch2: 5A/div (Bottom). Time scale: 5  $\mu$ s/div.

**Fig. 19.** Measured waveforms of  $V_{S1}$ ,  $i_{S2}$ ,  $i_{S2}$  collector-emitter voltage  $V_{S1}$  (Ch1: 100V/div); collector current  $i_{S1}$  (Ch2: 5A/div) (Top); collector-emitter voltage  $V_{S2}$  (Ch1: 100V/div); collector current  $i_{S2}$  (Ch2: 5A/div) (Bottom). Time scale: 4  $\mu$ s/Div.

used in the existing topologies [5, 6, 11-13] than in the proposed topology. The proposed converter has much better efficiency with a fewer number of auxiliary devices, and voltage and current stresses are lesser than the existing topologies. The overall efficiency of the proposed converter is 96.2% while operating at a maximum output power of 250W.

# **VIII. CONCLUSION**

This article proposes a novel interleaved buck DC-DC converter with high step-down conversion ratios. This converter utilizes a simple auxiliary cell to facilitate soft-switching conditions for the main switching devices. The operational principles and design analysis are discussed. To validate the PLECS simulation results, a laboratory prototype is developed and experimental investigations are performed on a 200 V-60 V converter system. The experimental tests are

# Electrica 2024; 24(3): 767-779 Bhajana et al. Soft-Switching Interleaved DC-DC Converter

TABLE III. COMPARISON OF EXISTING CONVERTERS WITH PROPOSED CONVERTER

|          | NS | NL   | NC | ND | $f_{\rm s}({ m kHz})$ | $V_{\rm in}$ | V <sub>o</sub> | <i>P</i> <sub>o</sub> (W) | ss  | TD | Efficiency |

|----------|----|------|----|----|-----------------------|--------------|----------------|---------------------------|-----|----|------------|

| [5]      | 4  | 2    | 5  | 2  | 40                    | 400          | 25             | 400                       | No  | 13 | 93.36%     |

| [6]      | 2  | 1,1* | 2  | 2  | 125                   | 100          | 50             | 300                       | Yes | 8  | 95%        |

| [11]     | 3  | 1,1* | 3  | 2  | 50                    | 20           | 12             | 72                        | No  | 10 | 96.4%      |

| [12]     | 3  | 3    | 3  | 2  | 50                    | 20           | 12             | 72                        | No  | 11 | 96.3%      |

| [13]     | 6  | 1,2* | 2  | _  | 100                   | 48           | 1.2            | 400                       | Yes | 11 | 93.3%      |

| Proposed | 2  | 4    | 3  | 4  | 40                    | 200          | 60             | 250                       | Yes | 13 | 96.13%     |

$f_{sr}$ , switching frequency; NC, number of capacitors; ND, number of diodes; NL, number of inductors; NS, number of switches;  $P_{or}$  output power; SS, soft-switching; TD, total device count;  $V_{inr}$  input voltage;  $V_{or}$  output voltage.

conducted up to 250W output power and confirm the soft-switching ability of the proposed converter without introducing additional stresses. The key advantages of these converters include reduced switching losses, a reduced number of devices, and enhanced efficiency.

**Availability of Data and Materials:** The data that support the findings of this study are available on request from the corresponding author.

**Peer-review:** Externally peer-reviewed.

**Author Contributions:** Concept – V.V.S.K.B.; Design – V.V.S.K.B.; Supervision – P.D.; Resources – V.K.; Materials – V.V.S.K.B.; Data Collection and/or Processing – V.V.S.K.B., P.B.; Analysis and/or Interpretation – V.V.S.K.B., P.B.; Literature Search – V.V.S.K.B., P.B.; Writing- V.V.S.K.B., Critical Review – P.D., V.K.

**Declaration of Interests:** The authors have no conflict of interest to declare.

**Funding:** The authors declared that this study has received no financial support.

# **REFERENCES**

- P.-L. Wong, P. Xu, P. Yang, and F. C. Lee, "Performance improvements of interleaving VRMs with coupling inductors," *IEEE Trans. Power Electron.*, vol. 16, no. 4, pp. 499–507, 2001. [CrossRef]

- K.-W. Ma, and Y.-S. Lee, "A novel uninterruptible DC-DC converter for UPS applications," Conference Record of the 1991 IEEE Industry Applications Society Annual Meeting, vol. 1, pp. 1074–1080, 1991. [CrossRef]

- Y. Tian, Z. Li, H. Liu, Y. Liu, and M. Ban, "High-performance wireless charging system using interleaved buck converter and integrated solenoid magnetic coupler," *IEEE Trans. Transp. Electrif.*, vol. 9, no. 3, pp. 3821–3835, 2023. [CrossRef]

- C.-T. Tsai, and C.-L. Shen, "Interleaved soft-switching buck converter with coupled inductors," in IEEE International Conference on Sustainable Energy Technologies, 2008, pp. 877–882. [CrossRef]

- C.-T. Pan, C.-F. Chuang, and C.-C. Chu, "A novel transformerless interleaved high step-down conversion ratio DC-DC converter with low

- switch voltage stress," *IEEE Trans. Ind. Electron.*, vol. 61, no. 10, pp. 5290–5299, 2014. [CrossRef]

- S.-S. Lee, "Step-down converter with efficient ZVS operation with load variation," *IEEE Trans. Ind. Electron.*, vol. 61, no. 1, pp. 591–597, 2014. [CrossRef]

- L. Jiang, C. C. Mi, S. Li, C. Yin, and J. Li, "An improved soft-switching buck converter with coupled inductor," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 4885–4891, 2013. [CrossRef]

- 8. H. Ghojavand, and E. Adib, "A single-switch soft-switched high step-down zeta converter with low output current ripple," *IEEE Trans. Power Electron.*, vol. 38, no. 4, pp. 5024–5031, 2023. [CrossRef]

- M. Ilic, and D. Maksimovic, "Interleaved zero-current-transition buck converter," *IEEE Trans. Ind. Appl.*, vol. 43, no. 6, pp. 1619–1627, 2007. ICrossRefl

- D.-T. Do, H. Cha, B. L.-H. Nguyen, and H.-G. Kim, "Two-channel inter-leaved buck LED driver using current-balancing capacitor," *IEEE J. Emerg. Sel. Top. Power Electron.*, vol. 6, no. 3, pp. 1306–1313, 2018. [CrossRef]

- M. Biswas, S. Majhi, and H. Nemade, "Performance of a coupled inductor for interleaved buck converter with improved step-down conversion ratio," IET Power Electron., vol. 14, no. 2, pp. 239–256, 2021. [CrossRef]

- M. Biswas, S. Majhi, and H. Nemade, "Two-phase high efficiency interleaved buck converter with improved step-down conversion ratio and low voltage stress," *IET Power Electron.*, vol. 12, no. 15, pp. 3942–3952, 2019. [CrossRef]

- A. Asghari, "An expandable ZVZCS high step-down interleaved DC-DC converter," *IEEE Trans. Power Electron.*, vol. 38, no. 12, pp. 15589–15602, 2023. ICrossRefl

- M. Amiri, H. Farzanehfard, and E. Adib, "A nonisolated ultrahigh step down DC-DC converter with low voltage stress," *IEEE Trans. Ind. Electron.*, vol. 65, no. 2, pp. 1273–1280, 2018. [CrossRef]

- R. Pashaie, M. Sabahi, and E. Babaei, "An interleaved high step-down coupled inductor based quadratic DC-DC converter," *IET Power Electron.*, vol. 16, no. 9, pp. 1558–1572, 2023. [CrossRef]

- M. Dalla Vecchia, G. Van den Broeck, S. Ravyts, J. Tant, and J. Driesen, "A family of DC–DC converters with high step-down voltage capability based on the valley-fill switched capacitor principle," *IEEE Trans. Ind. Electron.*, vol. 68, no. 7, pp. 5810–5820, 2021. [CrossRef]

- 17. A. G. Ghamsari Esfahani, and E. Adib, "Very high step-down coupled inductor two-phase buck converter with single magnetic element and inherent clamp voltage capability," *IET Power Electron.*, vol. 17, no. 5, pp. 640–648, 2024. [CrossRef]

<sup>\*</sup>Coupled inductors.

# Electrica 2024; 24(3): 767-779 Bhajana et al. Soft-Switching Interleaved DC-DC Converter

Veera Venkata Subrahmanya Kumar Bhajana received his B.E. degree in Electronics and Communication Engineering from Sapthagiri College of engineering, India (University of Madras) in 2000, an M.E. degree from the P.S.N.A College of Engineering and Technology under Anna University in 2005, and PhD in Electrical Engineering from Bharath University, India in 2011. He was previously associated as a post-doctoral researcher at the University of West Bohemia, Pilsen, Czech Republic from August 2013 to June 2015. He is currently working as an Associate Professor in the School of Electronics Engineering at KIIT (Kalinga Institute of Industrial Technology) University, Bhubaneswar, India since December 2011.

Pravat Biswal was born in Bhubaneswar, India. He received the B.Tech. degree in electrical engineering from the C.V. Raman College of Engineering at Bhubaneshwar, Odisha, India,in 2008,and the M.Tech. degree from NIT Warangal, specializing in power electronics and drives, in 2011. He is currently a Ph.D. Research Scholar and an Assistant Professor with KIIT University, Odisha.

Pavel Drabek received his M.S. and PhD degrees in electrical in electrical engineering from the University of West Bohemia (UWB), Pilsen, Czech Republic, in 2000 and 2004, respectively. From 2003 to 2005, he was a Design Engineer with the company Alltronic, Ltd., Pilsen. In 2005, he joined the UWB as an Assistant Professor at the Department of Electromehanics and power electronics, Faculty of Electrical Engineering. His main research interests include soft-switching inverters, AC-AC converters, multilevel converters, and electromagnetic compatibility of power electronic converters.

Vijay Kakani received the B.Sc. degree in electronics and communication engineering from Jawaharlal Nehru Technological University, Kakinada, India, in 2012, the M.Sc. degree in computers and communication systems from the University of Limerick, Ireland, in 2014, and the Ph.D. degree in information and communication engineering and future vehicle engineering from Inha University, South Korea, in 2020. Currently, he is an Assistant Professor in the Department of Integrated System Engineering, School of Global Convergence Studies, Inha University. His research interests include autonomous vehicles, sensor signal processing, applied computer vision, deep learning, systems engineering, and machine vision applications.