# A 1GS/s, 9-bits DAC Interleaved (2+1)-bit Then 2-bit per Cycle SAR ADC

# Salma El-Sawy, Ahmet Tekin 🕩

Department of Electrical Engineering, Özyeğin University, İstanbul, Turkey

Cite this article as: El-Sawy S, Tekin A. A 1GS/s, 9-bits DAC Interleaved (2+1)-bit Then 2-bit per Cycle SAR ADC. Electrica, 2020; 20(2): 153-158.

#### **ABSTRACT**

This study presents a high-speed successive-approximation-register analog-to-digital converter (SAR ADC) for low-noise low-power satellite transceiver applications. The proposed system is a (2+1)-bit then 2-bit per cycle SAR ADC with a sampling rate of 1 GS/s, 9-bits resolution designed in a 65-nm standard CMOS process. This system resolves nine bits using a special switching scheme in a total of four cycles per sample. This is achieved by interleaving four capacitive digital to analog converter (C-DACs) with 1-fF unit capacitance. As the interleaving is limited only to the DACs that match well, the design is not affected by the drawbacks of full interleaving. Hence, better power efficiency and performance metrics were obtained in comparison to regular interleaved ADCs. A special timing with an additional first bit comparator is optimized to have appropriate timing margins for every step from a single 4-GHz low-noise clock source that is readily available in the 8-GHz direct conversion frontend. This comparator is reused as the active comparator in both the interleaving phases. The proposed design achieved an effective number of bits value of 8.2 bits at Nyquist rate with a power consumption of 12 mW, resulting in a figure of merit of 38.37 fJ/conversion-step.

Keywords: ADC, high-speed, SAR

#### Introduction

Successive-approximation-register analog-to-digital converters (SAR ADCs) were previously confined to medium-speed, medium-resolution applications as iterative sequential schemes required at least n number of cycles to resolve n number of bits. However, advances in technology and the various innovative architectures in the field made it possible to push the speed limits of the SAR ADC from hundreds of MS/s to few GS/s. Several approaches have been introduced to enhance the capabilities of SAR ADCs used for higher frequency applications. Moreover, SAR ADCs are considered as more power efficient than FLASH and pipeline as SAR ADCs depend primarily on digital logic and a single comparator that is considered to be the only active analog block in the circuit. Some systems incorporate asynchronous systems to eliminate any idle conversion time [1-4]. Differential SAR ADCs [1-3] are preferred over single-ended topologies [4] to enhance the linearity and to balance any possible mismatch. Differential SAR ADCs are achieved by doubling the capacitive DAC and increasing the switching power. The disadvantage associated with differential SAR ADCs in terms of power consumption was addressed by designing a monotonic switching scheme that resolves the same number of bits with less number of switching steps [1, 2]. Hence, this switching scheme has decreased the power consumption and reduced the area by half by excluding the MSB binary capacitor and resolving the first bit while sampling. However, it may severely suffer from the dynamic changes in the input common mode seen by the comparators. A trilevel monotonic switching SAR ADC [5] addressed the disadvantage of variations due to dynamic input common mode and suggested a switching scheme that keeps the input common mode voltage of the comparator constant.

Researchers have shown keen interest in interleaving SAR ADCs to resolve the speed constraint of single-stage ADCs; they increased the sampling speed by n number of interleaved stages. This was achieved by doubling the area and the power [6-9]. Although time interleav-

# **Corresponding Author:**

Ahmet Tekin

Ahmet.tekin@ozyegin.edu.tr

Received: 06.05.2020 Accepted: 25.05.2020

DOI: 10.5152/electrica.2020.20048

Content of this journal is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License.

ing is widely used to enhance the speed, the linear relation between the sampling speed and the number of stages can result in lower performance due to channel-to-channel mismatches, thus limiting the number of stages that can be used. Some researchers have proposed the use of an extra channel for calibration [7], which is a less-preferred solution for low-power applications.

Another approach was introduced to increase the sampling rate using single-stage ADCs; multiple bits were resolved per cycle rather than 1 bit at a time. In the meantime, multi-bits-per-cycle SAR ADCs have been an area of interest to researchers [6], [10-13]. Multi-bit-per-cycle SAR ADCs can achieve higher

frequencies with less power, area, and circuit complexity compared with interleaving SAR ADCs with the only disadvantage of high power consumption due to the additional comparators. Reference [3] introduced a system that resolves 1-bit then 2-bit per cycle via top plate sampling method. The first bit can be identified immediately after sampling without waiting for any pre-charge operation.

The present study introduces an unconventional design technique based on (2+1)-bit then 2-bit per cycle SAR ADC with

Figure 1. Block diagram of the proposed system

interleaving capacitive DACs, avoiding the complexity, high power consumption, and channel mismatches of conventional, fully interleaved SAR ADCs. The proposed method shown in Figure 1 significantly enhances the speed–resolution tradeoffs via multi-bit cycling with special timing and an additional comparator. The rest of the paper is organized as follows. Section II provides a detailed explanation of the system architecture and switching scheme. Section III describes circuit implementation for various sub-blocks. Simulation results and performance metrics of the proposed system are presented in Section IV, and Section V concludes the study.

#### **Proposed SAR ADC Architecture and Switching Scheme**

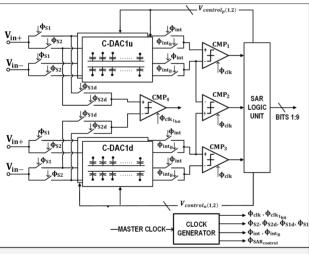

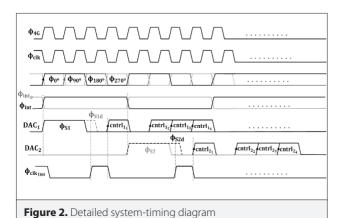

Timing of the proposed (2+1)-bit then 2-bit per cycle SAR ADC with interleaving DAC is shown in Figure 2. The system block diagram is illustrated in Figure 1. It primarily comprises four differential binary weighted DACs for bit cycling operation, three comparators for defining the four regions of comparison needed to resolve two bits at a time, and an additional comparator that operates at one fourth of the master-clock frequency to identify the first bit. Moreover, sampling switches, DAC interleaving switches, a synchronization block, and a SAR control unit are required to control the capacitive DAC operation to dump the equivalent charge based on the decision at the previous step.

#### **System Architecture**

The main advantage of this work is that interleaving the DACs reduces the number of comparators and sampling duration without any significant change in performance and power consumption. This approach has additional advantages: it increases the sampling period and addresses the settling-time constraint for the most significant first conversion step. The two DACs; DAC1,  $DAC_{2}$ , are interleaved with the clocks  $\phi_{int}$  and  $\phi_{int}$ . Taking  $DAC_{1}$  as an example, when clock  $\phi_{int}$  is low, it is disconnected from the backend cycling comparator system. Simultaneously, clock  $\phi_{\rm sl}$ turns on for the sampling phase to take place, where the input is differentially sampled on the top plates of DAC, array while all their bottom plates are recharged to common mode voltage  $(V_{cm})$ . Meanwhile, DAC<sub>1</sub> is connected to the first bit comparator (CMP<sub>4</sub>) when  $\phi_{s_1d}$  clock is high. The signal  $\phi_{s_1}$  goes low slightly earlier, allowing the sampling node to settle and hold. Then,  $\phi_{clk}$ is fired to take the first bit decision; this switch should be disconnected from the sampling node before dumping any charge to avoid voltage degradation resulting from charge distribution. On the contrary, DAC, executes the 2-bit-at-a-time resolving scheme through the backend cycling comparators. When clock  $\phi_{\text{ints}}$  goes high, the DAC<sub>1</sub> array is connected to this backend comparator array to start resolving two bits at a time with cntrl<sub>1,3,4</sub> rising edges, as shown in Figure 2. DAC, repeats the same operation with  $\phi_{\rm int}$  clock in control of sampling; then, 1-bit resolution when  $\phi_{int}$  goes low, followed by 2-bit cycling until a total of nine bits are resolved.

# **Timing and Switching Scheme**

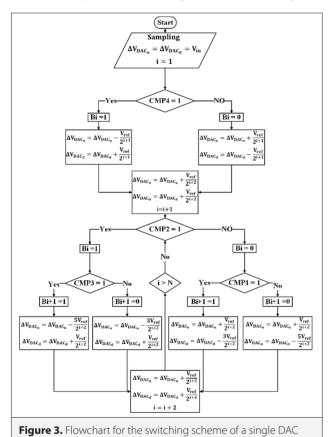

The timing diagram illustrated in Figure 2 shows the control signals of every block in the system. A 4-GHz master clock is available in the system. A timing block is implemented to generate a 1-GHz clock in its four phases used to sample the output bits at the speed of two bits per rising edge of each of the four phases of the clock. Moreover, a 500-MHz clock is needed to control the interleaving switch and generation of the control signals for each SAR control unit controlling the interleaving DACs. The conversion sequence of this SAR logic is summarized in Figure 3.

### **Circuit Implementations**

This section discusses the details of the circuit blocks.

### Sampling and Interleaving Switches

Sampling switches are considered as one of the most critical blocks for high-speed ADC applications. The sampling switch

Table 1. Font sizes and styles

| Publication                   | [6]<br>IJSSC'18 | [10]<br>ISCAS'14 | [11]<br>CICC'17 | This<br>Work                       |

|-------------------------------|-----------------|------------------|-----------------|------------------------------------|

| Architecture                  | 2XTI -2b<br>SAR | SAR              | SAR             | (2+1)<br>then 2b<br>SAR –DAC<br>TI |

| Technology                    | 28 nm           | 65 nm            | 40 nm           | 65 nm                              |

| Supply(V)                     | 0.9             | 1.2              | 1.2             | 1.25                               |

| Resolution                    | 7 bits          | 8 bits           | 10 bits         | 9 bits                             |

| $f_s$ (GS/s)                  | 2.4             | 0.4              | 0.3             | 1                                  |

| Unit Cap. (F)                 | -               | 2.5f             | 0.5f            | 1f                                 |

| Total Cap. (F)                | 64f             | 4*640f           | 935*0.5f        | 4*256f                             |

| Power (mW)                    | 5               | 5.6              | 2.1             | 12                                 |

| Figure of merit (fJ/convstep) | 25.3            | 67f              | 19              | 38.374                             |

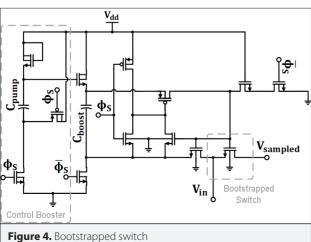

linearity plays a crucial role in defining the overall linearity of the system. Thus, it should be carefully designed for good overall linearity. The ON resistance of NMOS switches is dependent on the source gate voltage ( $V_{\rm GS}$ ); this makes this resistance dependent on the input signal. This dependency can be expressed using Equation (1). Moreover, the threshold voltage  $V_{\rm th}$  of the sampling device also depends heavily on the input voltage.

$$R_{nmo s_{on}} = \frac{1}{\mu_n C_{ox} \frac{W}{L} (V_G(t) - V_{in}(t) - V_{th}(t))}$$

(1)

Bootstrapped switch scheme was implemented to provide a constant  $V_{\rm GS}$  (across the bootstrapped switch) as high as Vdd, keeping the value of "ON" resistance constant [14] and ensuring linear performance for the switch design shown in Figure 4. The proposed system comprises three clocked switches: sampling switches, 1st bit sampling switches, and interleaving switches. All the three are bootstrapped switches with sizes proportional to their sampling capacitance.

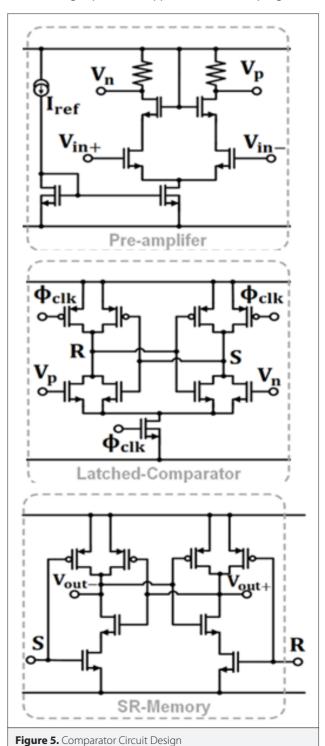

# Comparator

A schematic of the comparator is shown in Figure 5. It is a latched comparator with a high-speed pre-amplifier with low-offset diff-pair cascode gain. This stage is designed for a fixed current of 800 uA per comparator. The 1K ohm load resistors belonging to the four comparator preamplifiers are used as a trim point during power-up single-time DC offset calibration.

#### **Simulation Results**

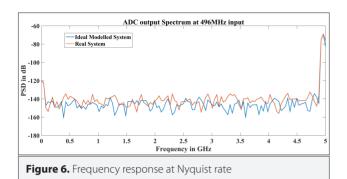

The entire system is simulated using Cadence CAD tool along with the extracted capacitive DAC array to include the parasitic effects. Figure 6 shows the output spectrum of the ADC at full Nyquist rate; Figure 7 shows the response to a 66.4-MHz input.

# Conclusion

The performance summary of the proposed design are summarized in Table 1; the results of previous experiments are included in the table for reference. An untraditional SAR approach proposed in this study provided a unique opportunity for a low-power, robust ADC design in a 65-nm CMOS circuit with simple quadrature clock phases. Utilizing only one additional comparator and by doubling up the passive C-DACs with corresponding interleaved timing, an effective number of bits value of 8.2 bits was achieved with total current consumption of <10mA from a single power supply of 1.25 V.

Peer-review: Externally peer-reviewed.

Conflict of Interest: The authors has no conflicts of interest to declare.

**Financial Disclosure:** The authors declared that the study has received no financial support.

#### References

- C. Liu, S. Chang, G. Huang, Y. Lin, "A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure", IEEE Journal of Solid-State Circuits, vol. 45, no. 4, pp. 731-740, 2010. [Crossref]

- T. V. Cao, S. Aunet, T. Ytterdal, "A 9-bit 50MS/s Asynchronous SAR ADC in 28nm CMOS", NORCHIP 2012, Cpenhagen, 2012, pp. 1-6.

- Q. Fan, J. Chen, "A 10-bit 400 MS/s Asynchronous SAR ADC Using Dual-DAC Architecture for Speed Enhancement," 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWS-CAS), Boston, MA, 2017, pp. 583-586. [Crossref]

- A. Ashraf, S. Ashraf, N. Z. Rizvi, S. A. Dar, "Low Power Design of Asynchronous SAR ADC," 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Chennai, 2016, pp. 4214-4219. [Crossref]

- J. Zhao, N. Mei, Z. Zhang, L. Meng, "Vaq-Based Tri-level Switching Scheme for SAR ADC," Electronics Letters, vol. 54, no. 2, pp. 66-68, 2018. [Crossref]

- C. Chan, Y. Zhu, W. Zhang, S. P. U, R. P. Martins, "A Two-Way Interleaved 7-b 2.4-GS/s 1-Then-2 b/Cycle SAR ADC with Background Offset Calibration," IEEE Journal of Solid-State Circuits, vol. 53, no. 3, pp. 850-860, March 2018. [Crossref]

- C. Lin, Y. Wei and T. Lee, "A 10-bit 2.6-GS/s Time-Interleaved SAR ADC With a Digital-Mixing Timing-Skew Calibration Technique," in IEEE Journal of Solid-State Circuits, vol. 53, no. 5, pp. 1508-1517, 2018. [Crossref]

- W. Kim, H. Kong, Y. Roh, H. Kang, S. Hwang, D. Jo, D. Chang, M. Seo, S. Ryu, "A 0.6 V 12 b 10 MS/s Low-Noise Asynchronous SAR-Assisted Time-Interleaved SAR (SATI-SAR) ADC," IEEE Journal of Solid-State Circuits, vol. 51, no. 8, pp. 1826-1839, 2016. [Crossref]

- D. Stepanovic and B. Nikolic, "A 2.8 GS/s 44.6 mWTime-Interleaved ADC Achieving 50.9 dB SNDR and 3 dB Effective Resolution Band-

- width of 1.5 GHz in 65 nm CMOS," IEEE Journal of Solid-State Circuits, vol. 48, no. 4, pp. 971-982, 2013. [Crossref]

- G. Dai, C. Chen, S. Ma, F. Ye, J. Ren, "A 400-MS/s 8-b 2-b/cycle SAR ADC with Shared Interpolator and Alternative Comparators," 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne VIC, 2014, pp. 2365-2368. [Crossref]

- J. Song, X. Tang, N. Sun, "A 10-b 2b/cycle 300MS/s SAR ADC with a Single Differential DAC in 40nm CMOS," 2017 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, 2017, pp. 1-4. [Crossref]

- Y. Lien, "A 4.5-mW 8-b 750-MS/s 2-b/step Asynchronous Subranged SAR ADC in 28-nm CMOS technology," 2012 Symposium on VLSI Circuits (VLSIC), Honolulu, HI, 2012, pp. 88-89. [Crossref]

- C. Chan, Y. Zhu, I. Ho, W. Zhang, S. U, R. P. Martins, "16.4 A 5mW 7b 2.4GS/s 1-then-2b/cycle SAR ADC with Background Offset Calibration," 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, 2017, pp. 282-283. [Crossref]

- P. Tadeparthy, M. Das, "Techniques to Improve Linearity of CMOS Sample-and-hold Circuits for Achieving 100 dB Performance at 80 MSps," 2002 IEEE International Symposium on Circuits and Systems. Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 2002, pp. V-V.

# Electrica 2020; 20(2): 153-158 El-Sawy and Tekin. Successive Approximation Register Analog to Digital Converter

Salma El-Sawy was born in Egypt, received her B.Sc. from Ainshams University (Egypt) Faculty of Engineering, Electronics and Communication Department in 2013. In 2014, she joined CST Middle east as a verification and research engineer. She moved to Istanbul and joined Özyegin University Electrical and Electronics Engineering department in 2017 to pursue her M.Sc. degree. Her main interests include circuit design, analog and mixed signal integrated circuit design.

Ahmet Tekin has received his EE PhD degree from University of California Santa Cruz, CA, EE MS degree from North Carolina A&T State University, Greensboro, NC and EE BS degree from Bogazici University, Istanbul, Turkey in 2008, 2004, and 2002, respectively. In addition to academic research in microelectronics, he worked for multiple innovative semiconductor design companies such as; Multigig, Inc., Newport Media, Aydeekay LLC, Broadcom corp., Semtech Corp., Nuvoton Technology Corp., Qualcomm and Waveworks Inc., leading designs for communications, consumer and medical markets. His main focus area is analog/RF/mixed-signal integrated circuit design for communication and biomedical applications. He is currently head of Analog&RF Labs at Özyeğin University and serves in the board of directors of Waveworks Inc, Mission Viejo, CA.