# Modeling and Analysis of Positive Output Luo Converter in Voltage Control Mode

Premalatha Kaliannan<sup>1</sup>, Nandhini Jyothi<sup>2</sup>, Kavitha Rangasamy<sup>1</sup>

<sup>1</sup>Kumaraguru College of Technology, Coimbatore, TamilNadu, India <sup>2</sup>Sri Ramachandra Institute of Higher Education and Research, Chennai, India

Cite this article as: Kaliannan, N. Jyothi, K. Rangasamy, "Modeling and Analysis of Positive Output Luo Converter in Voltage Control Mode", Electrica, vol. 21, no. 2, pp. 259-271, May, 2021.

#### **ABSTRACT**

This paper presents the modeling, controller design, and stability analysis for positive output LUO converter (POLC) in voltage control mode. The POLC uses elementary voltage lift technique to regulate the output voltage from a variable input voltage. In modeling of POLC, the transfer functions for control input to output and disturbance input to output are derived using linearized state-space averaging technique. The developed transfer function of POLC is analyzed for various duty cycles and circuit parameters. To improve the dynamic performance of POLC, the integral lead controller and the integral lag-lead controller are designed. This paper also presents the maximum time delay computation of POLC without losing small signal stability. Rekasius's substitution was used to analyze the stability with time delay. The performance of both the controllers was analyzed for various input voltages, reference voltages, and loads in MATLAB Simulink environment. The integral lag-lead controller provided an improved transient response and better stability. To validate the performance of the controllers, prototype experimental setup was implemented. The performance of the integral lag-lead controller was better despite the time delay caused by feedback element.

Keywords: Integral lag-lead controller, positive output LUO converter, Rekasius's substitution, stability, state space averaging techniques, time delay

#### Introduction

Renewable energy sources such as solar PV, wind energy, and fuel cell, and so forth, are extensively used for generation of electrical power due to the depletion of fossil fuels, global warming, and the effects of greenhouse gas emissions. The output voltage from most renewable sources is in the form of direct current (DC) [1-4]. Hence, DC-DC converters are employed to interface source and load. The basic topologies of DC-DC converters such as buck, boost, and buck-boost converters have been proposed to regulate the output voltage of the system under consideration. The effects of parasitic elements in fundamental converters restrict the output voltage and conversion efficiency [5-9]. The recently developed converters such as Luo converters are widely used for the control and conversion of power [10, 11]. One of the most efficient converters among Luo converters is the positive output Luo converter (POLC), which provides large conversion ratio, high power density, high efficiency, positive output voltage, and low ripple content [12-14]. To design a controller for DC-DC converter, proper mathematical model of the converter and its response are required [15, 16]. The mathematical model of the converter completely describes the behaviour of the system due to disturbances and variations in control signals. Many control algorithms and mathematical models of DC-DC converters using Laplace transform and Z transform have been proposed in the previous literature [17, 18]. Generally, DC-DC converters have power semiconductor switches and diodes, which are nonlinear in nature. The dynamic model of the power electronic converters can be described using state-space modeling. State-space averaging and small-signal linearization technique provides an effective solution for the application of control techniques to DC-DC converters [19, 20]. The state-space modeling, design, and analysis of controllers are simple for the basic power converters topologies. However, recent converters require complex mathematical models [21-24]. Time delays have become an issue in the dynamic analysis of the POLC while measuremeing the output voltage for feedback. The maximum time delay is the minimum time required for the converter to operate in a stable

## **Corresponding Author:**

Premalatha Kaliannan

E-mail:

kppremalatha@gmail.com

Received: August 26, 2020 Accepted: January 28, 2021

**Available Online Date:**

May 20, 2021

**DOI:** 10.5152/electrica.2021.20069

Content of this journal is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License.

region. The estimation of time delay has been introduced in the literature [25227], but the algorithm is considerably complex.

In this paper, the linearized small signal state-space averaging model and transfer functions of POLC are derived. Using transfer functions, the open loop stability of the converter is analyzed using step response and root locus plots. This paper also describes the computation of maximum time delay of the converter without losing the small signal stability using Rekasius's substitution theorem and Routh stability criterion. The characteristic equation of dynamic system with transcendental term cannot be solved by analytical method. Rekasius's substitution converts the characteristic equation of the converter with transcendental term into polynomial equation. The maximum time delay and the roots at which crossing the imaginary axis is computed using the Routh Hurwitz criterion. The integral lead and lag-lead controllers have been designed for POLC, and their dynamic performance is analyzed for sudden changes in input voltage, reference voltage, and load. The prototype model has been developed to validate the simulation results.

This paper is organized as follows: In continuation to this introduction, Section II presents the design and working of the converter along with the details of formation of state-space equations, state-space averaging, small-signal linearization, and transfer function formulation. In Section III, the performance of the converter is analyzed using time response plots in open-loop modes. This section also emphasizes on the design of controllers, time delay computation, and stability analysis of POLC. Section IV presents the hardware implementation of the converter. Section V discusses the conclusion of the proposed work.

# **Mathematical Modeling of POLC**

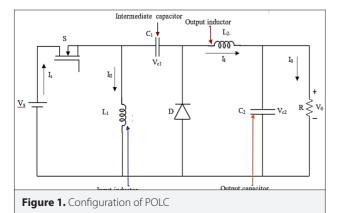

The structure of POLC is shown in Figure 1. POLC configuration allows only unidirectional power flow, that is, from source to load. The converter output can be regulated based on the control signal and perturbations in input voltage and circuit parameters. The MOSFET is used as a power switch, which operates either in conduction mode or in blocking mode. A time-dependent switching variable 'd' is used to describe the switching states. When d=1, the switch is in ON state; when d=0, the switch is in OFF state.

The following assumptions are considered for the analysis: The switches are in ideal condition, and conduction of the converter is in continuous mode; the initial voltage across the capacitor is zero. The variables  $V_s$  and  $V_o$  are the input and output voltages of the converter, respectively.

In general, the state-space representation of the converter is given by

$$\dot{x} = A_i x + B_i u$$

$$y = C_i x$$

where state vector  $x = [i_{l1} i_{l2} v_{c1} v_{c2}]^T$ .

A<sub>i</sub>-State-space matrix: i = 1 when switch S is ON and i = 0 when switch S is OFF. B<sub>i</sub>-Input matrix and C<sub>i</sub>- Output matrix.  $v_o = v_{c2} = [0001]$ . There are two inputs (disturbance input and control input), namely  $u = [V_i d]^T$ .

When the switch S is ON, the diode D is reverse biased and the corresponding state equations are

$$v_S = L_1 \frac{di_{l1}}{dt} \tag{1}$$

$$v_s - v_{c1} - v_{c2} = L_2 \frac{di_{l2}}{dt} \tag{2}$$

$$C_1 \frac{dv_{c1}}{dt} = i_{L2} \tag{3}$$

$$C_2 \frac{dv_{c2}}{dt} = i_{L2} - \frac{v_0}{R} \tag{4}$$

$$A_{1} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & \frac{1}{L_{2}} & \frac{-1}{L_{2}} \\ 0 & \frac{-1}{c_{1}} & 0 & 0 \\ 0 & \frac{1}{c_{2}} & 0 & \frac{-1}{RC_{2}} \end{bmatrix}, B_{1} = \begin{bmatrix} \frac{1}{L_{1}} & 0 \\ \frac{1}{L_{2}} & 0 \\ 0 & 0 \\ 0 & 0 \end{bmatrix}, C_{1} = \begin{bmatrix} 0 & 0 & 0 & 1 \end{bmatrix}$$

When the switch S is OFF, the diode D will conduct and the corresponding state equations are

$$v_{c1} = -L_1 \frac{di_{l1}}{dt} \tag{5}$$

$$v_{c2} = -L_2 \frac{di_{l2}}{dt} \tag{6}$$

$$C_1 \frac{dv_{c1}}{dt} = i_{L1} \tag{7}$$

$$A_{0} = \begin{bmatrix} 0 & 0 & \frac{-1}{L_{1}} & 0\\ 0 & 0 & 0 & \frac{-1}{L_{2}}\\ \frac{1}{C_{1}} & 0 & 0 & 0\\ 0 & \frac{1}{C_{2}} & 0 & \frac{-1}{RC_{2}} \end{bmatrix}, B_{0} = [0], C_{0} = [0\ 0\ 0\ 1]$$

$$(8)$$

To achieve the final state-space equations of POLC, averaging of state-space matrices A, B, and C are given by

$$A = A_1 d + A_0 (1 - d) (9)$$

$$B = B_1 d + B_0 (1 - d) (10)$$

$$C = C_1 d + C_0 (1 - d) (11)$$

Using equations (1)–(11), the final state-space equations obtained are

$$L_1 \frac{di_{l1}}{dt} = (d-1)v_{C1} + dv_s \tag{12}$$

$$L_2 \frac{di_{l2}}{dt} = dv_{C1} - v_{C2} + dv_s \tag{13}$$

$$C_1 \frac{dv_{c1}}{dt} = (1 - d)i_{l1} - di_{l2} \tag{14}$$

$$C_2 \frac{dv_{c2}}{dt} = i_{l2} - \frac{v_0}{R} \tag{15}$$

$$A = \begin{bmatrix} 0 & 0 & \frac{d-1}{L_1} & 0 \\ 0 & 0 & \frac{d}{L_2} & \frac{-1}{L_2} \\ \frac{(1-d)}{c_1} & \frac{-d}{c_1} & 0 & 0 \\ 0 & \frac{1}{C_2} & 0 & \frac{-1}{BC_2} \end{bmatrix} B = \begin{bmatrix} \frac{d}{L_1} & 0 \\ \frac{d}{L_2} & 0 \\ 0 & 0 \end{bmatrix}, C = [0 \ 0 \ 0 \ 1]$$

#### Small signal linearization of state equations

The time-varying state equations (12) to (15) can be linearized using small-signal perturbation technique. The duty cycle and input voltage are represented by the addition of DC quantities and superimposed small alternating current (AC) signal variations.

By adding variations in the duty cycle and input voltage, the modified duty cycle and input voltage are given as,

$$d = D + \hat{d}$$

,  $v_s = V_s + \hat{v}_s & 1 - d = 1 - D - \hat{d}$

which causes changes in the state and output of the converter. Hence, variations in the inductor voltage, capacitor current, and output voltage are

$$\frac{di_l}{dt} = \frac{d(l_l + \hat{t}_1)}{dt} \tag{16}$$

$$\frac{dv_c}{dt} = \frac{d(V_c + \hat{v}_c)}{dt} \tag{17}$$

$$v_0 = V_0 + \hat{v}_0 \tag{18}$$

Substituting the variations in equation (12) to (15), the statespace equations become

$$L_1 \frac{d(I_{l1} + \widehat{U_{l1}})}{dt} = -(1 - D - \hat{d})(V_{C1} + \widehat{v_{C1}}) + (D + \hat{d})(V_S + \widehat{v_S})$$

(19)

$$L_2 \frac{d(I_{12} + \widehat{I_{12}})}{dt} = -(D + \hat{d})(V_{C1} + \widehat{v_{C1}}) - (V_{C2} + \widehat{v_{C2}}) + (D + \hat{d})(V_s + \widehat{v_s})$$

(20)

$$C_1 \frac{d(V_{c1} + \widehat{v_{c1}})}{dt} = (1 - D - \hat{d})(i_{l1} + \widehat{i_{l1}}) + (D + \hat{d})(i_{l2} + \widehat{i_{l2}})$$

(21)

$$C_2 \frac{d(V_{c2} + \widehat{v_{c2}})}{dt} = i_{l2} + \widehat{\iota_{l2}} - \frac{(V_0 + \widehat{v_0})}{R}$$

(22)

The above equations are simplified based on the derivative of a constant term and the product of two AC terms. The product of two AC terms gives second-order nonlinear terms and are assigned to zero. The product of an AC term and a DC term is a DC quantity, and therefore, it is linear. The linearized and simplified state equation is of the form

$$\widetilde{x(t)} = \widetilde{A}\widetilde{x(t)} + \widetilde{B_1}\,\widehat{v_s} + \widetilde{B_C}\widehat{d}$$

and is given as

$$\begin{bmatrix} \frac{\widehat{dt}_{l_1}}{dt} \\ \frac{\widehat{dt}_{l_2}}{dt} \\ \frac{\widehat{dv}_{c_1}}{dt} \\ \frac{\widehat{dv}_{c_2}}{dt} \end{bmatrix} = \begin{bmatrix} 0 & 0 & \frac{-(1-D)}{L_1} & 0 \\ 0 & 0 & \frac{D}{L_2} & -\frac{1}{L_2} \\ \frac{1-D}{C_1} & -\frac{D}{C_1} & 0 & 0 \\ 0 & \frac{1}{C_2} & 0 & -\frac{1}{RC_2} \end{bmatrix} \begin{bmatrix} \widehat{t}_{11} \\ \widehat{t}_{12} \\ \widehat{v}_{c_1} \end{bmatrix} + \begin{bmatrix} \frac{D}{L_1} \\ \frac{D}{L_2} \\ 0 \\ 0 \end{bmatrix} \widehat{v}_S + \begin{bmatrix} \frac{V_S}{L_1(1-D)} \\ \frac{V_S}{L_2(1-D)} \\ -\frac{DV_S}{RC_1(1-D)^2} \\ 0 \end{bmatrix} \widehat{d}$$

(23)

$$\widehat{v_0} = \widetilde{\mathcal{C}x(t)} \tag{24}$$

#### **Transfer functions**

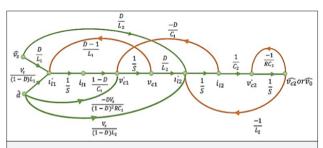

To derive continuous current mode transfer functions, Signal flow graph was drawn using the linearized small signal equations from (19)–(22), as shown in Figure 2. The four state variables are nodes of the graph. Inputs of the signal flow are and control input. The nodes are connected by branch gains as in equations (19)–(22). The transfer functions between input signals and output signal were obtained using Mason's gain formula and are listed in Table 1.

#### **Performance Analysis**

For the analysis of converter in voltage control mode, two inputs namely, disturbance input voltage - and the control input were considered. The POLC was modeled and simulated in Simulink MATLAB environment and their corresponding results are presented with and without controllers.

The specifications of POLC are listed in Table 2 and are considered for the analysis.

Figure 2. Signal flow graph of POLC

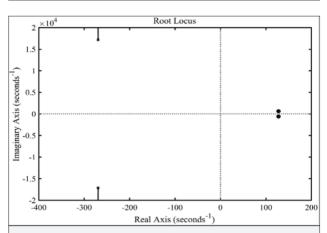

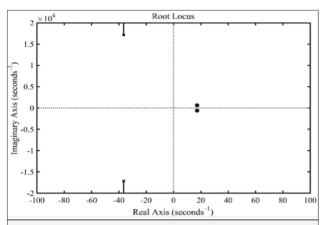

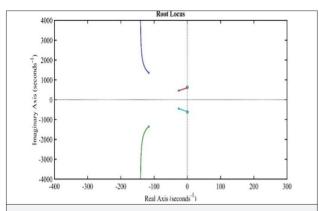

**Figure 3.** Root locus plot of output to control input transfer function for D=0.6

# **Table 1.** Transfer functions of POLC $\frac{\hat{v}_0(s)}{\hat{d}(s)}$

Transfer functions of output voltage to control input

No. of forward paths K = 3

$$\begin{aligned} \text{(i)} \ P_1 &= \frac{v_s \, D}{L_1 L_2 C_1 C_2} \frac{1}{S^4} \\ \text{(ii)} \ P_2 &= \frac{-D^2 V_s}{L_2 C_2 R C_1 (1-D)^2} \frac{1}{S^3} \\ \text{(iii)} \ P_3 &= \frac{V_s}{(1-D) L_2 C_2} \frac{1}{S^2} \end{aligned} \qquad \qquad \Delta_1 = 1 \\ \Delta_2 &= 1 \\ \Delta_3 = 1 + \frac{(1-D)^2}{L_1 C_1} \frac{1}{S^2}$$

Loop gains:

$$L_1 = -\frac{(1-D)^2}{L_1C_1}\frac{1}{S^2}; L_2 = -\frac{1}{L_2C_2}\frac{1}{S^2}; L_3 = -\frac{D^2}{L_2C_1}\frac{1}{S^2}L_4 = -\frac{1}{SRC_2}$$

Non touching loop gains

$$G_{od} = \frac{v_0(S)}{\hat{d}(S)} = \frac{\frac{V_S}{(1-D)L_2C_2}}{S^4 + \frac{S^3}{RC_2} + S^2 \left(\frac{D^2}{L_2C_2} + \frac{1}{L_2C_2} + \frac{(1-D)^2}{L_1C_1}\right) + S\left(\frac{D^2}{RL_2C_1} + \frac{(1-D)^2}{L_1C_1}\right) + S\left(\frac{D^2}{RL_2C_1} + \frac{(1-D)^2}{RL_2C_1} + \frac{(1-D)^2}{L_1C_1}\right) + S\left(\frac{D^2}{RL_2C_1} + \frac{(1-D)^2}{RL_2C_1} + \frac{(1-D)^2}{L_1C_1}\right)}$$

(25)

Transfer function of output voltage to disturbance input voltage  $\frac{\hat{v}_0(s)}{\hat{v}_s(s)}$

No. of forward paths K = 2

$$\begin{aligned} \text{(i) } P_1 &= \frac{(1-D)D^2}{L_1L_2C_1C_2}\frac{1}{S^4} \\ \text{(ii) } P_2 &= \frac{D}{L_2C_2}\frac{1}{S^2} \end{aligned} \qquad \qquad \Delta_1 = 1 \\ \Delta_2 &= 1 + \frac{(1-D)^2}{L_1C_1} \cdot \frac{1}{S^2}$$

Loop gains

$$L_1 = -\frac{(1-D)^2}{L_1 C_1} \frac{1}{S^2}; L_2 = -\frac{1}{L_2 C_2} \frac{1}{S^2}; L_3 = -\frac{D^2}{L_2 C_1} \frac{1}{S^2} L_4 = -\frac{1}{SRC_2}$$

Non touching loop gains:

$$L_3L_4 = \frac{D^2}{RL_2C_1C_2} \frac{1}{S^3}; L_1L_4 = \frac{(1-D)^2}{RL_1C_1C_2} \frac{1}{S^3}; L_1L_2 = \frac{(1-D)^2}{L_1C_1L_2C_2} \frac{1}{S^4}$$

$$G_{os} = \frac{\hat{v}_{o}(s)}{\hat{v}_{s}(s)} = \frac{\frac{D}{L_{2}C_{2}} s^{2} + \frac{D(1-D)}{L_{1}L_{2}C_{1}C_{2}}}{s^{4} + \frac{S^{3}}{RC_{2}} + S^{2} \left(\frac{D^{2}}{L_{2}C_{1}} + \frac{(1-D)^{2}}{L_{1}C_{2}} + \frac{(1-D)^{2}}{L_{1}C_{1}}\right) + S\left(\frac{D^{2}}{RL_{2}C_{1}} + \frac{(1-D)^{2}}{RL_{1}C_{1}C_{2}}\right) + \frac{(1-D)^{2}}{L_{1}C_{1}L_{2}C_{2}}}$$

(26)

Table 2. Parameters of POLC

| Parameter                                   | Value          |

|---------------------------------------------|----------------|

| Inductors: L <sub>1</sub> , L <sub>2</sub>  | 36.04 mH       |

| Capacitors: C <sub>1</sub> , C <sub>2</sub> | 21.40, 30.4 μF |

| Load Resistance: R                          | 135.2 Ω        |

| Power                                       | 600 W          |

| Input Voltage - V <sub>s</sub>              | 90–150 V       |

| Output Voltage - V <sub>0</sub>             | 260 V          |

# Output to control input transfer function $\frac{\hat{p}_0(s)}{\hat{d}(s)}$

The transfer function of the converter was developed using the values provided in Table 2 and equation (25) for duty ratio of D = 0.6 and is given by

$$\frac{\hat{v}_0(s)}{\hat{d}(s)} = \frac{2.923*10^9 S^2 - 7.471*10^{10} S + 1.139*10^{14}}{S^4 + 284 S^3 + 2.937*10^9 S^2 - 7.457*10^{10} S + 1.14*10^{14}}$$

(27)

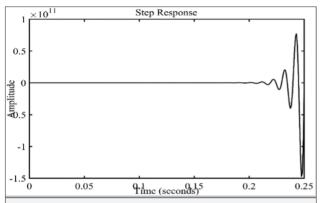

The root locus plot of the above transfer function is shown in Figure 3. Two complex poles lie on left half of s-Plane, and two

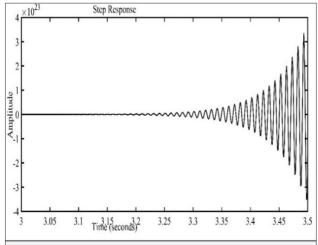

complex poles and two complex zeros lie on the right half of s-Plane. The step response plot is shown in Figure 4. The output of the system continuously increased with time. Hence, the system was concluded to be unstable.

When the load resistance value R was changed from 135.2 W to 1000 W, the corresponding transfer function became

$$\frac{\hat{v}_0(s)}{\hat{d}(s)} = \frac{2.923 * 10^9 S^2 - 7.471 * 10^{10} S + 1.139 * 10^{14}}{S^4 + 28.4S^3 + 2.937 * 10^7 S^2 - 7.457 * 10^9 S + 1.14 * 10^{14}}$$

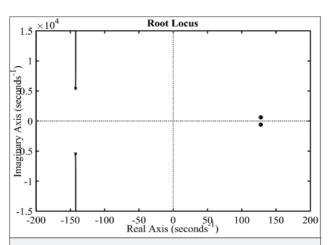

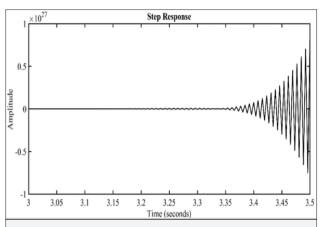

The transfer function has four complex poles and two complex zeros and is shown in Figure 5. Two complex poles lie on the left-hand side (LHS) and another two poles lie on the right-hand side (RHS). The complex zeros also lie on the RHS. The two complex poles and zeros moved slightly on the LHS but never crossed the origin. Hence, the system was completely unstable, and the corresponding step response is given in Figure 6. When the load resistance value is increased, the complex poles moves towards the imaginary axis. This makes the system less stable.

When the capacitor value  $C_2$  was changed to 360  $\mu F$  from 30.4  $\mu F$  and on time of the MOSFET was changed to D = 0.3, the transfer function became

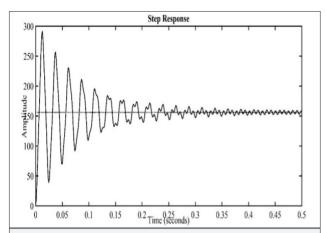

**Figure 4.** Step response of output to control input transfer function for D=0.6

**Figure 5.** Root locus plot of output to control input transfer function for D = 0.6 and R = 1000  $\Omega$

**Figure 6.** Step response of output to control input transfer function for D = 0.6 and R = 1000  $\Omega$

$$\frac{\hat{v}_0(s)}{\hat{d}(s)} = \frac{2.923 * 10^9 S^2 - 7.471 * 10^{10} S + 1.139 * 10^{14}}{S^4 + 28.4S^3 + 2.937 * 10^7 S^2 - 7.457 * 10^9 S + 1.14 * 10^{14}}$$

The transfer function had two complex poles and two zeros. Two poles and zeros lie on the RHS plane, as shown in Figure 7.

**Figure 7.** Root locus plot of output to control input transfer function for D = 0.3 and  $C_2 = 360 \mu F$

**Figure 8.** Step response plot of output to control input transfer function for D = 0.3 and  $C_2$  = 360  $\mu f$

This indicates that the system is unstable. The system response is shown in Figure 8.

# Output to disturbance input transfer function $\frac{\hat{v}_0(S)}{\hat{v}_c(S)}$

For  $L_1 = L_2 = 36.04$  mH,  $C_1 = 29.04$   $\mu$ F,  $C_2 = 260$   $\mu$ F and D = 0.6, the input to output transfer function using equation (26) is given by

$$\frac{\hat{v}_0(s)}{\hat{v}_s(s)} = \frac{5.845 * 10^4 S^2 + 2.278 * 10^{10}}{S^4 + 28.4 S^3 + 6.624 * 10^5 S^2 + 1.439 * 10^7 S + 3.796 * 10^{10}}$$

This transfer function has four poles and two zeros. The four poles lie on the LHS plane, and the zeros lie on the imaginary axis. The corresponding root locus and step response are shown in Figure 9 and Figure 10, respectively. The step response of the system seems to be stable, but it has ripples and there is a steady state error.

From the above analysis, it can be inferred that the system is unstable due to the presence of RHS plane zeros and poles of the system even when the duty cycle or the circuit parameters are changed. To improve the stability and transient behaviour of the system, integral lead controller was considered.

**Figure 9.** Root locus plot of output to disturbance input transfer function for D = 0.6

**Figure 10.** Step response plot of output to disturbance input transfer function for D = 0.6

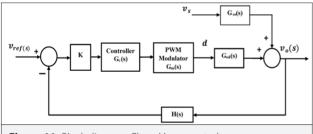

Figure 11. Block diagram: Closed loop control

#### Closed loop analysis of the converter

The main objective of the closed loop system is to design a suitable controller to make the system more stable and to maintain the desired output voltage when perturbations are introduced in the input voltage from 90 to 130 V.

The open-loop transfer function with integral lead controller for D = 0.6 is given as

$$G(S) = \frac{2.63 \times 10^8 S^3 + 5.565 \times 10^{10} S^2 + 7.108 \times 10^{13} S + 4.789 \times 10^{16}}{S^6 + 74444 S^5 + 3.515 \times 10^6 S^4 + 1.075 \times 10^{10} S^3 + 1.182 \times 10^{12} S^2 + 2.087 \times 10^{15} S}$$

The open-loop transfer function with integral lead lag controller for D = 0.6 is given as

**Figure 12.** Step response of the system with integral lead controller

$$G(S) = \frac{2.057*10^7S^4 + 4.597*10^{10}S^3 + 2.422*10^{13}S^2 + 1.247*10^{16}S + 1.142*10^{19}}{S^7 + 7584S^6 + 4.557*10^6S^5 + 1.124*10^{10}S^4 + 2.682*10^{12}S^3 + 1.253*10^{15}S^2 + 2.522*10^{17}S}$$

The controller is designed to meet the time domain specifications such as damping factor of 0.7, settling time of 60 ms, and an overshoot of 6%. The block diagram of the closed-loop voltage-controlled converter is shown in Figure 11.

The AC component of the output voltage of the converter is given as

$$v_0(s) = \frac{KG_c(s)G_m(s)G_{od}(s)}{1 + KG_c(s)G_m(s)G_{od}(s)H(s)} v_{ref}(s) + \frac{KG_{os}(s)}{1 + KG_c(s)G_m(s)G_{od}(s)H(s)} v_s(s)$$

where

$G_{c}(S)$  - Transfer function of the controller

$G_m(S)$  - Modulator gain = 0.125

H(S) - Feedback gain = 26

While analyzing the performance of the controller, the change in disturbance input was assumed to zero.

#### Integral lead controller design

To reduce the DC gain and increase the margin of stability, the integral lead controller is required to achieve high gain at low frequencies. The pole at origin provided a phase lag of  $90^{\circ}$  at all frequencies. The lead controller was designed to compensate the phase lag and to increase the speed of response. At low frequency f < 476 rad/s and at high frequency f > 7143 rad/s, the phase angle was approximately  $-90^{\circ}$ . The maximum phase angle contributed by the lead controller was  $60^{\circ}$  at 1843 rad/s, which is a geometric mean of pole and zero frequencies.

The transfer function of the controller was

$$G_c(s) = \frac{0.068(1 + 0.0021s)}{s(1 + 0.00014s)}$$

The open-loop transfer function of the system was

$$G(s) = G_c(s) * G_m(s) * G_{od}(s) * H(s)$$

The step response of the closed system for duty ratio of D=0.6 is shown in Figure 12.

The controller provides the settling time of 120 ms, and there are oscillations in the transient response. After that, it follows the reference value. The step response indicates that the system is stable, but the high value of settling indicates that the system response is sluggish.

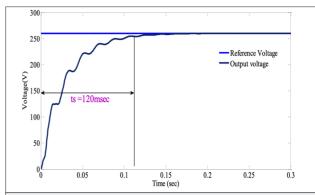

#### Integral lag-lead controller design

To improve the speed of response and relative stability of the converter, an integral lag-lead controller is proposed. The controller provides high gain and phase lag of -90° at low frequencies. The gain of the controller is 0.1. There is no intersection between the responses of the controller. The two zeros are placed at  $f_{z1}$ =0.892 KHz and  $f_{z2}$ =8 KHz. The poles are located at  $f_{p1}$ =7.142 KHz and  $f_{p2}$ =0.14 KHz. To get a faster response, the value of  $f_{z2}$  is set high and is nearly 10 times of the value of  $f_{z1}$ . The pole at the origin and the other two poles minimize the steady state error to zero and improve the speed of response.

The transfer function of the integral lag-lead controller is

$$G_c(s) = \frac{0.1(1 + 0.001121s)(1 + 0.000125s)}{s(1 + 0.00014s)(1 + 0.00714s)}$$

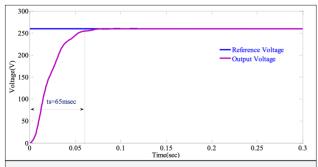

The step response plot for the closed loop system with integral lag-lead controller is shown in Figure 13. The integral lag-lead controller provides settling time of 65 ms with negligible overshoot for duty ratio of D=0.6. The reduced value of settling time indicates that the speed of response of the system is improved.

#### Time delay analysis

This section presents the time delay analysis of POLC where the time delay element is introduced in the feedback. If all the roots of the characteristic equation lie on the LHS of the complex S-plane, the delayed linear system is asymptotically stable. However, the characteristic has many roots that result in high computation burden.

To compute the delay margin and analyze the stability of the system, it is necessary to obtain its characteristic equation with integral lag-lead controller. The characteristic equation is of the form

$$1 + KG_c(s)G_m(s)G_{od}(s)H(s)e^{-s\tau} = 0$$

or  $\Delta(s,\tau) = A(S) + B(S)e^{-s\tau} = 0$  (27)

**Figure 13.** Step response of the system with integral lag-lead controller

where  $\tau$ -Time delay. A(S) and B(S) are the polynomials of the characteristic equation having coefficients in terms of S and parameters of POLC.

$$A(S) = a_7 S^7 + a_6 S^6 + a_5 S^5 + a_4 S^4 + a_3 S^3 + a_2 S^2 + a_1 S + a_0$$

$$B(S) = b_4 S^4 + b_3 S^3 + b_2 S^2 + b_1 S + b_0$$

Coefficients of the polynomial depends on the converter parameters, controller gain, and delay.

The main objective is to study the location of roots of the characteristic equation using Rikasius's substitution [26]. The Rikasius's substitution converts the transcedental equation into polynomial equation. The Rikasius's substitution is  $e^{-s\tau} = \frac{1-ST}{1+ST}$ ,  $\tau \in R$ ,  $T \in R$ , which is defined for the imaginary axis  $S = j \omega$ ,  $\omega \in R$ , the roots are on the imaginary axis.

This exact transformation holds if and only if

$$\tau = \frac{2}{\omega}(tan^{-1}(\omega\tau) + k\frac{\pi}{2}$$

where k = 0, 1, 2, ...

By substituting.  $e^{-s\tau}$  value in equation (27), we obtain

$$\Delta(s,\tau) = A(S) + B(S)(\frac{1 - ST}{1 + ST}) = 0$$

$$\Delta(s,\tau) = A(S)(1 + ST) + B(S)(1 - ST) = 0$$

(28)

The equation is of the form

$$\Delta(s,\tau) = p_8 S^8 + p_7 S^7 + p_6 S^6 + p_5 S^5 + p_4 S^4 + p_3 S^3 + p_2 S^2 + p_1 S + p_0 = 0$$

where

$p_8 = T, p_7 = 1 + 7584T,$

$p_6 = 7584 + 4.557 * 10^6T$

$p_5 = 4.557 * 10^6 + 1.122 * 10^10T$

$p_4 = 1.126 * 10^10 + 2.641 * 10^12T$

$p_3 = 2.733 * 10^12 + 1.25 * 10^15T$

$p_2 = 1.255*10^15 + 1.3973*10^17T$

$p_1 = 1.65 * 10^{17} - 1.241 * 10^19T$

$p_0 = 1.241 * 10^19$

After Rekasius's substitution, the characteristic changes into eighth-order polynomial.

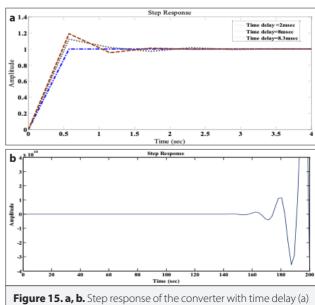

Now, the Routh stability criterion can be used to find the roots of the equation. The maximum time delay is computed from the Routh table as  $T_{max} = 8.7472$  ms.

The crossing frequency of imaginary axis is found by equating  $S^2$  row of Routh array to zero, i.e.,  $2.308*10^15 S^2 + 1.142*10^19=0$ , solving  $\pm j\omega = \pm j70$  rad/s. The time delay is in the order of ms, as the proposed system does not have any communication network. The time delay occurs only due to the measurement.

When the time delay exceeds 8.7472 ms, the system is unstable, that is, it loses its small signal stability. The theorectical time delay calculation is verified using time response plots.

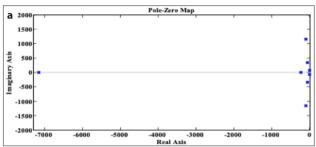

Figure 14a shows the pole zero plot of the characteristic equation with time delay  $\tau=8.8$  ms. All the roots of the characteristic equation lie on the LHS of the complex S-plane, and the

corresponding step response is shown in Figure 15a. The response attains the steady-state value without error. However, when delay t is added, the transient response increases linearly rather than exponentially. The time delay component modifies the nature of transient response of the system. Overshoot increases as the time delay increases. When the delay is less than the critical value,  $t = t_{max} = 8.7472$  ms, the system is stable.

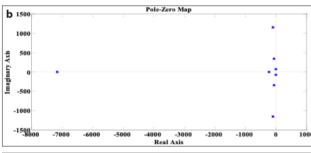

Figure 14b shows the pole zero plot of the characteristic equation with time delay  $\tau = \tau_{max} = 8.7472$  ms. The complex conjugate pair of roots located on the imaginary axis of the complex S plane. Hence, the system is mariginally stable.

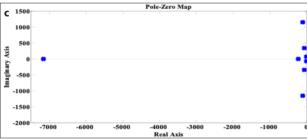

If the delay ( $\tau = 9$  ms) exceeds the maximum limit slightly, the system no longer remains stable. The complex conjugate pair

Figure 14. a-d. Pole-zero plot of the converter. (a) time delay = 8 ms (b) time delay = 8.747208 ms (c) time delay = 9 ms (d) expanded view of (c) near origin

of roots moving on to the RHS of the complex S-plane is shown in Figure 14c and d. For  $\tau = 9$  ms, magnitude of step response increases abruptly and is shown in Figure 15b. Hence, the system is unstable.

#### Steady-state performance

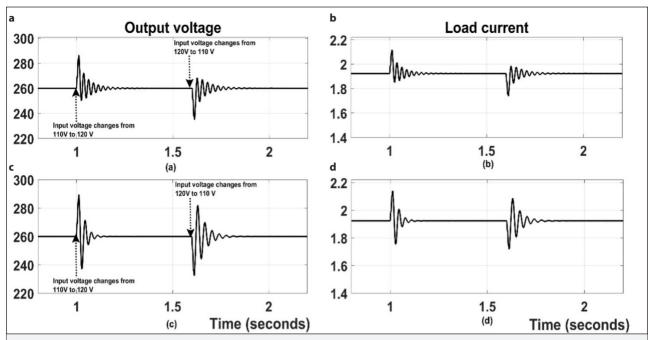

#### Sudden change in input voltage

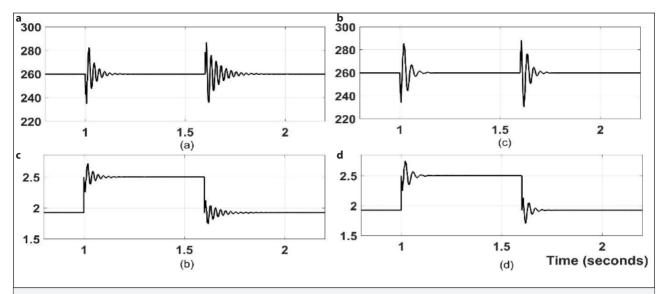

The steady-state performance is analyzed for varying input voltage with integral lead and lag-lead controller, as shown in Figure 16. The figure is plotted for output voltage and load current as a function of time. The output voltage is 260 V for the input voltage of 110 V, and the duty ratio evaluated by the controller is 0.71. The load current obtained is 1.9 A. At time t = 1 s, the input voltage is increased to 120 V, the output voltage is maintained as the reference value of 260 V. At t = 1.6 s, the input voltage is changed from 120 V to 110 V, and the corresponding output is 260 V. The output voltage and load current with integral lead controller is more oscillatory than the integral laglead controller. For perturbation in input, the output voltage takes 160 ms to settle at its steady state for integral lead controller, whereas the settling time is 60 ms for integral lag-lead controller. The overshoot of 60/260 = 23% and 17/260 = 6.61% are observed for integral lead and integral lag-lead controller, respectively. The steady state error is negligible in both cases.

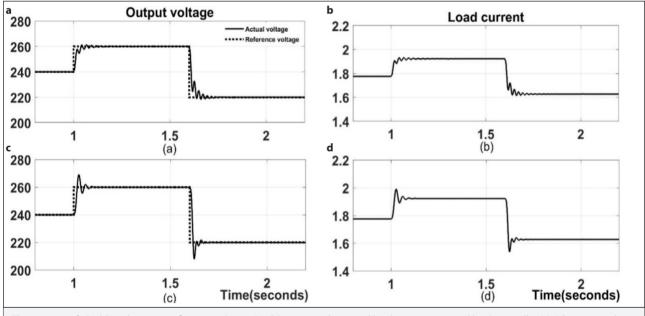

## Sudden change in reference voltage

The steady state performance is analyzed for varying reference voltage, as shown in Figure 17. At time t = 1 s, the reference voltage is increased to 260 V from 240 V for the constant input voltage of 120 V. The converter output voltage tracks the reference voltage with negligible overshoot and steady-state error. The duty ratio varies from 0.667 to 0.686. The load current varies from 2.39 A to 2.61 A. At time t = 1.6 s, the reference voltage is changed from 260 V to 240 V, and the converter fol-

time delay = 2 ms, 8 ms, and 8.3 ms (b) time delay = 8.8 ms

Figure 16. a-d. Simulated response of sudden change in input voltage -POLC (a), (b)-output voltage and load current - integral lead controller (c), (d) output voltage and load current - integral lag-lead controller

Figure 17. a-d. Sudden change in reference voltage -(a), (b) output voltage and load current - integral lead controller (c), (d) output voltage and load current - integral lag-lead controller

lows the reference value. After perturbation in reference, the voltage and load current response of integral lead controller is overdamped and it takes 160 ms to settle at its reference value. The voltage and load current response with integral lag-lead controller is underdamped and it takes 50 ms to settle at its reference value. On comparing the responses, the response of POLC with the integral lag-lead controller is faster than that with the integral lead controller.

# Sudden change in load resistance

The performance of the converter is analyzed for varying load resistance by keeping the reference voltage as 260 V and the input voltage as 120 V, as shown in Figure 18. Initially, the load resistance value is 135.2  $\Omega$ .

At time t=1 s, the load resistance value is changed to 104  $\Omega$ , and at time t=1.6 s, the load resistance is changed to 135.2  $\Omega$

**Figure 18. a-d.** Simulated response of sudden change in load resistance -(a), (b) – output voltage and load current - integral lead controller (c),(d) output voltage and load current - integral lag-lead controller

**Table 3.** Performance comparison

| Parameter     | Integral lead<br>controller | Integral lag-lead<br>controller |

|---------------|-----------------------------|---------------------------------|

| % Overshoot   | 24                          | 6.61                            |

| Settling time | 160 ms                      | 60 ms                           |

again. While reducing the resistance, the load current increases to 2.5 A and the overshoot is observed as 22/260 = 8.46% with negligible steady-state error for both controller design. When the load resistance is increased, the output voltage and load current responses take 220 ms to settle at its reference value for integral lead controller, whereas the settling time of integral lag-lead controller is 120 ms.

On comparing the performances of two controllers, the integral lag-lead controller gives better transient as well as steady-state performance (Table 3). The settling of the output voltage is 600 s to reach its steady-state value of 260 V using the MPPT algorithm is reported in [1].

**Figure 20.** Open loop mode (x axis: time (20 µs/div), y axis: Channel 1-Input voltage (10 V/div); Channel 2-output voltage (10 V/div); Channel 3-Control pulse 5 V/div)

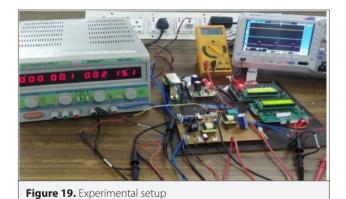

#### **Experimental Results**

A prototype model of POLC was constructed to validate the simulation results. The photograph of the experimental setup is shown in Figure 19.

The power switches were implemented by MOSFET-IRF540, which is driven by gate driver IC-TLP250. The switching frequency is set to 20 KHz. The control algorithm was implemented using dsPIC, and the gate pulses for power switch were produced based on the difference between the reference voltage and actual voltage.

The input voltage could vary from 12 V to 30 V, and the maximum load current ( $R_L$  = 135.5 W) was chosen for the controller design. To validate the simulation results, the prototype was implemented. The POLC was tested under open loop mode for the fixed input voltage of 15 V with varying duty ratio. The corresponding output voltage waveforms are shown in Figure 20.

ratio < 0.5 (x axis: time (20 µs/div), y axis: Channel 1-Input voltage (10 V/div); Channel 2-output voltage (10 V/div); Channel 3-Control pulse 5 V/div)

The output voltage changed with change in input voltage without controller. By incorporating the controller, the output voltage was maintained as constant at 24 V for variation in input voltage, as shown in Figure 21.

#### Conclusion

The modeling and analysis of voltage-controlled POLC with closed loop control is presented for different circuit parameters. The transfer functions of the converter are derived in detail (24, 25) using linearized state-space averaging technique. The integral lead controller and lag-lead controller are designed. Time delay analysis is carried out for the proposed controller using Rekasius's substitution and Routh stability criterion. The time delay value is in the order of milliseconds, as the delay is due to the measuring device. The integral lag-lead controller offers good closed loop system dynamics even when perturbations are present in input voltage and load when compared with the integral lead controller (Table 3). Furthermore, a prototype model is developed, and its results are incorporated.

**Peer-review:** Externally peer-reviewed.

**Author Contributions:** Concept – P.K., N.J., K.R.; Design – P.K., N.J., K.R.; Supervision – P.K., N.J., K.R.; Resources – P.K., N.J., K.R.; Materials – P.K., N.J., K.R.; Data Collection and/or Processing – P.K., N.J., K.R.; Analysis and/or Interpretation – P.K., N.J., K.R.; Literature Search – P.K., N.J., K.R.; Writing Manuscript – P.K., N.J., K.R.; Critical Review – P.K., N.J., K.R.

**Conflict of Interest:** The authors have no conflicts of interest to declare.

**Financial Disclosure:** The authors declared that this study has received no financial support.

#### References

- S. A. Amirtharaj, L. Premalatha, "Design of an Efficient Positive Output Self-Lift and Negative Output Self-Lift Luo Converters using Drift Free Technique for Photovoltaic Applications", Energy Procedia, vol. 117, pp. 651-657, Jun 2017. [Crossref]

- K. Sundareswaran, V. Vigneshkumar, P. Sankar, S. P. Simon, P. S. Rao Nayak, S. Palani, "Development of an Improved P&O Algorithm Assisted through a Colony of Foraging Ants for MPPT in PV System", IEEE Trans. Industrial Inform., vol. 12, no. 1, pp. 187-200, 2016. [Crossref]

- Z. Shan, S Liu, F. Luo, "Investigation of a Super-Lift Luo-Converter used in solar panel system", IEEE Int. Conf. Electricity Distribution, 2012. https://ieeexplore.ieee.org/document/6508606. [Crossref]

- G. Sivasankar, K. Vidhyaa, E. Anitha, B. A. Kumar, P. Vairaprakash, "Application of LUO Converter and Multilevel Cascaded Converter for Grid Integration of Solar PV Systems", Int. Conf. Circuit, Power and Computing Technologies (ICCPCT), Mar 2016. https://ieeexplore.ieee.org/document/7530378. [Crossref]

- M. G. Villalva, J. R. Gazoli, E. Ruppert, "Comprehensive approach to modelling and simulation of photovoltaic arrays", IEEE Trans. Power Electron., vol.25, no.5, pp. 1198-1208, Mar 2009. [Crossref]

- L. A. C. Lopez, A. M. Leinhardt, "A simplified nonlinear power source for simulating PV panels", Power Electron. Specialist, Annual Conf. PESC, vol.4, pp. 1729-1734, Aug 2003.

- M. G. Villalva, R. Gazoli, E. Ruppert, "Modelling and circuit simulation of photovoltaic arrays", Journal of Power Electron., vol.14, no.1, pp. 35-45, 2009. [Crossref]

- 8. T. Esram, P. L. Chapman, "Comparison of photovoltaic array maximum power point tracking techniques", IEEE Trans. Energy Con., vol.22, no.2, pp. 439-449, May 2007. [Crossref]

- L. Kumar, S. Jain, "A novel multiple input DC-DC converter for electric vehicular applications", IEEE Transportation electrification conference, pp. 1-6, Jun 2012. https://ieeexplore.ieee.org/document/6243427. [Crossref]

- A. Lidozzi, L. Solero, "Power balance control of multiple-input DCDC power converter for hybrid vehicles", IEEE Int. Symposium on Ind. Elect., vol.2, pp. 1467-1472, May 2004. [Crossref]

- A. Sivaprasad, S. Kumaravel, S. Ashok, "Integration of Solar PV/Battery Hybrid System Using Dual Input DC-DC Converter", Int. Conf. on Power and Energy Systems, Jul 2016. https://ieeexplore.ieee. org/document/7516473. [Crossref]

- S. Saravanan, N. Ramesh Babu, "Performance Analysis of Boost & Cuk Converter in MPPT based PV system", Int. Conf. on Circuit, Power and Computing Technologies, Jul 2015. https://ieeexplore.ieee.org/document/7159425. [Crossref]

- S. Lakshmi, T. S. Renga Raja, "Design and implementation of an observer controller for a buck converter", Turkish Journal of Elect. and Comp. Engg., vol.22, pp. 562-572, Jan 2014. [Crossref]

- M. Shirazi, R. Zane, D. Maksimovic, "An auto-tuning digital controller for dc-dc power converters based on online frequency-response measurement", IEEE Trans. Power Electron., vol.24, no.11, pp. 2578-2588, Aug 2009. [Crossref]

- M. Ebrahimzadeh, A. Rahmati, "Adaptive and fast-response controller for boost PFC converter with wide range of operating conditions", IEEE Power Electron. & Drive Syst. Conf., pp. 157-162, May 2010. [Crossref]

- M. S. Jorge Alberto, P. Rodrigo Loera, H. Elvia Palacios, J. L. González-Martínez, "Modelling and control of a DC-DC quadratic

## Electrica 2021; 21(2): 259-271 Kaliannan et al. Modelling and Analysis of POLC in voltage Control Mode

- boost converter with R2P2", IET Power Electron., vol.7, no.1, pp. 11-22. 2012.

- A. Beccuti, S. Mariethoz, S. Cliquennois, S. Wang, M. Morari, "Explicit model predictive control of dc-dc switched-mode power supplies with extended kalman filtering", IEEE Trans. Indus. Electron., vol.56, no.6, pp. 1864-1874, Feb 2009. [Crossref]

- S. D. Saswati, N. Byamakesh, "Control analysis and experimental verification of a practical dc-dc boost converter", Journal of Elect. Systems and Information Tech., vol.2, pp. 378-390, Dec 2015. [Crossref]

- K. Mandal, A. Abdelali El, A. Abusorrah, M. Al-Hindawi, Y. Al-Turki, G. Damian, B. Soumitro, "Non-linear modelling and stability analysis of resonant DC-DC converters", IET Power Elect., vol. 8, no.12, pp. 2492-2503, Dec 2015. [Crossref]

- J. Morales, J. Leyva-Ramos, E. Carbajal, M. Ortiz-Lopez, "Average current-mode control scheme for a quadratic buck converter with a single switch", IEEE Trans. Power Electron., vol.23, no.1, pp. 485-490, Jan 2008. [Crossref]

- R. Leya, L. Martínez-Salamero, H. Valderrama-Blavi, J. Maixé, R. Giral, F. Guinjoan, "Linear state feedback control of a bost converter for large-signal stability", IEEE Trans. Circuits and Systems, vol.48, no.4, pp. 418-432, Mar 2001. [Crossref]

- M. Shirazi, R. Zane, D. Maksimovic, "An auto-tuning digital controller for dc-dc power converters based on online frequency-response measurement", IEEE Trans. Power Electron., vol.24, no.11, pp. 2578-2588, Dec 2009. [Crossref]

- R. L. Colalla, A. El aroudi, I. Queinnec, "Robust LQR control for PWM inverter: An LMI approach", IEEE Trans. Industrial Electron., vol. 56, no.7, pp. 2548-2558, 2009. [Crossref]

- B. Hekimoğlu, S. Ekinci, "Optimally Designed PID Controller for a DC-DC Buck Converter via a Hybrid Whale Optimization Algorithm with Simulated Annealing", Electrica, Vol.20, no.1, pp.19-27, Jan 2020. [Crossref]

- J. Chen, G. X. Gu, C. N. Nett, "A new method for computing delay margins for stability of linear delay systems", Systems & Control Letters, vol.26, no.2, pp.107-117, 1995. [Crossref]

- 26. H. R. Baghaee, M. Mirsalim, B. G. Gharehpetian, H. Ali Talebi, "A generalized descriptor-system robust H∞ control of autonomous microgrids to improve small and large signal stability considering communication delays and load nonlinearities", Electrical power and Energy Systems, vol.92, pp. 63-82, Nov 2017. [Crossref]

- A. Naveed, S. Sönmez, S. Ayasun, "Identification of Stability Delay Margin for Load Frequency Control System with Electric Vehicles Aggregator using Rekasius Substitution", IEEE Milan Power Technology.

## Electrica 2021; 21(2): 259-271 Kaliannan et al. Modelling and Analysis of POLC in voltage Control Mode

Dr. Premalatha Kaliannan was born in India in June, 1976. She received her BE, MTech, and PhD degrees from Madras, SASTRA, and Anna University in 1997, 2002, and 2016, respectively. Currently, she is working as Associate Professor in Kumaraguru College of Technology, Coimbatore, India. Her research interests include power quality, stability analysis of the converter, wind energy conversion systems, and electrical drives. She is a member of IE(I), ISTE, and SSI.

Ms. Nandhini Jyothi completed her BE and ME degrees from Anna University, Chennai. She is now working as Assistant Professor in Sri Ramachandra Institute of Higher Education and Research, Chennai, India. Her research interests include stability analysis and smart systems.

Dr. Kavitha Rangasamy completed her BE from Bharathiar University, India, ME from Anna University, and PhD degree from Anna University in 2001, 2004, and 2015, respectively. She has 17 years of teaching experience. She is now working as Associate Professor in Kumaraguru College of Technology, India. She is a life time member of ISTE. Her research interests include multilevel inverters and optimisation techniques.