# Analysis of a Modified Switching Pattern for Packed U Cell-15 Inverter Topology with Advanced Level Shift Carrier Pulse Width Modulation Techniques

Narendra Kumar Muthukuri 🕞, Subbarao Mopidevi 🕞

Vignan's Foundation for Science, Technology & Research, Guntur, India

Cite this article as: N. K. Muthukuri, S. Mopidevi, "Analysis of a Modified Switching Pattern for Packed U Cell-15 Inverter Topology with Advanced Level Shift Carrier Pulse Width Modulation Techniques", Electrica, vol. 21, no. 2, pp. 272-282, May, 2021.

#### **ABSTRACT**

This paper focused on the design and analysis of a modified switching sequence for a 15-level Packed U Cell (PUC-15) inverter. The proposed switching sequence improved the harmonic spectrum, reduced the burden on switches, and controlled the switching frequency. The performance of the inverter was also observed in terms of total harmonic distortion (THD) with constant frequency (phase disposition [PD] and phase opposition disposition [POD]) and variable frequency, variable frequency carrier opposition (VFCO) level shift triangular carrier-based sinusoidal pulse width modulation (SPWM) techniques at different modulation indices of M = 0.2, 0.4, 0.6, 0.8, and 1. Insights from the modified switching sequence and pulse width modulation techniques were analyzed and compared via simulations in a MATLAB/Simulink environment. By analyzing the results, it showed that the PD-PWM technique produced better results than other modulation techniques, and that the voltage and current THD% obtained therefrom 2.49% and 1.86% at M = 1, which comes under IEEE-519 standard.

**Keywords:** Multilevel inverter, packed U cell, phase disposition, phase opposition disposition, variable frequency, variable frequency carrier opposition, total harmonic distortion

#### **Research Motivation**

Power industries currently use inverters to convert power from one state of level into another. In power conversions, advanced multilevel inverters (MLI) influence various features as follows:

- 1. Lowering harmonic distortion

- 2. Using fewer switches with more levels

- 3. Staircasing outputs

- 4. Performing regulatory functions with fundamental, medium, and higher frequencies

- 5. Minimizing switching losses

- Providing transient electromagnetic interference (EMI) capability and high-quality power outputs

This study incorporated these features by modifying the existing control switching sequence for a packed U cell 15 (PUC-15) MLI. This modified switching sequence helped maintain harmonics results under IEEE-519 standard.

## Literature Review

MLIs are highly reliable components used in power semiconductor devices to convert power and compensate reactive power. MLIs are pre-owned to work effectively at high-power high-voltage and neutral-power neutral-voltage applications with an MLI strategic control structure of [1, 2]. Basic conventional MLIs are used to overcome the problems in 2-level multilevel inverters, which have high-order harmonics and are partially controlled using large capacitive filters. The first conventional MLIs were neutral-point clamped (NPC) inverters proposed by Nabae in 1981 [3] to overcome power electronic component stress, but this topology had several technical complications for higher-frequency operations and needed more clamping diodes level by level. Another conventional MLI by Meynard et al. [4] proposed fiber channel (FC) topology using capacitors, but these are uneconomical compared with diodes and have

### **Corresponding Author:**

Narendra Kumar Muthukuri

#### E-mail:

narendra.ee7@gmail.com

Received: September 22, 2020

Accepted: March 16, 2021

Available Online Date:

May 20, 2021

**DOI:** 10.5152/electrica.2021.20082

Content of this journal is licensed under a Creative Commons Attribution-NonCommercial 4.0 International License.

voltage balance problems across capacitors. Another conventional MLI by Mariusz Malinowski et al. [5] cascaded H-bridge (CHB) topology that required separate DC sources for each module and had increasing levels of complexity in operation, cost, and EMI. Therefore, researchers are working on modified and advanced multilevel inverter configurations like Packed U Cell [6-12], T-type [13], nested [14], and cross-switched T-type (CT-Type) [15]. This study provides insights into the recently introduced PUC MLI [16, 17].

We have identified that asymmetrical MLIs help control higher harmonic levels and develop transient output waveforms compared with symmetrical MLIs. Switching pressures at asymmetric MLIs are varied and low; however, symmetrical MLIs work the same with higher switching pressures for power semiconductor components. Moreover, asymmetrical MLIs have lower PSCs, lower switching pressure with higher output voltage levels, and lower order harmonics. The topology of the PUC has fewer switches with reduced device count of power components. Therefore, its overall efficiency increases with low stress on power switches, preventing the need for bulky installations because its transformer requires less construction. The main applications are power generation systems, industrial drives, and power quality improvements. Table 1 compares semiconductor components for different traditional multilevel inverters and 15-PUC MLI.

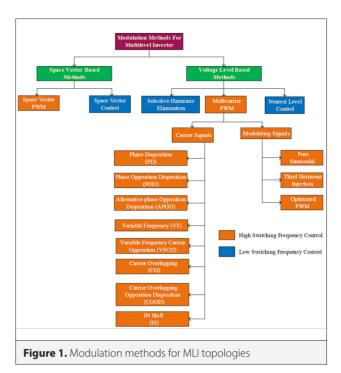

In reviewing the literature, we found that some 15-level inverters do not show perfect 15-level output voltages and show high harmonics [18-21]. The existing 15-level PUC inverters show uneven 15-level output voltages because of the usage of conventional switching sequences. Therefore, researchers are focusing on this problem to control harmonics at 15-level output voltages (above 0 at 7 levels, below 0 at 7 levels and the central level) with a modified switching sequence. The PUC MLIs are controlled using different constants and variable switching frequency pulse width modulation (PWM) controllers at different modulation indices (MI). Figure 1 shows the modulation methods for MLI topologies.

# **Contributions of This Study**

A modified switching sequence is proposed for PUC-15 to replace a conventional switching sequence for controlling switching pressures with lower harmonics.

**Table 1.** Semiconductor components for 15-level inverters

| Name              | NPC | FC | СНВ | НСНВ | PUC |

|-------------------|-----|----|-----|------|-----|

| Switches          | 28  | 28 | 28  | 12   | 08  |

| Diodes            | 26  | 0  | 0   | 0    | 0   |

| DC bus capacitors | 14  | 14 | 07  | 03   | 03  |

| Total components  | 68  | 42 | 35  | 15   | 11  |

FC: flying capacitor; CHB: cascaded H-bridge; PUC: packed U cell; NPC: neutral-point clamped; HCHB: hybridized cascaded H-bridge

- To control the PUC-15 MLI constant switching frequency carrier-based PWM method, phase disposition (PD) and phase opposition disposition (POD) techniques are analyzed at different MI of 0.2, 0.4, 0.6, 0.8, and 1.0.

- To control the PUC-15 variable switching frequency, a carrier-based PWM method is also analyzed with variable frequency (VF) and variable frequency carrier opposition (VFCO) techniques at different MI of 0.2, 0.4, 0.6, 0.8, and 1.0

- The performance of the modified switching sequence is analyzed and compared with the different PWM techniques at multiple modulation indexes and represented graphically.

In this article, we discuss mainly the following:

- Section I: Design and analysis of PUC-15 topology

- Section II: PWM techniques

- Section III: Simulation and theoretical result analysis

- Section IV: Performance analysis

- Sections V, VI, and VII: Conclusion, references, and nomenclature.

#### **Designing and Analysis of PUC-15 Topology**

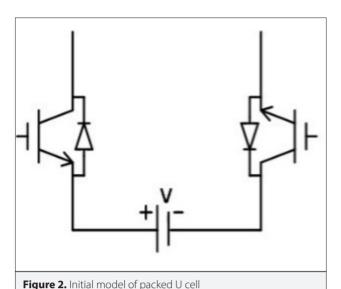

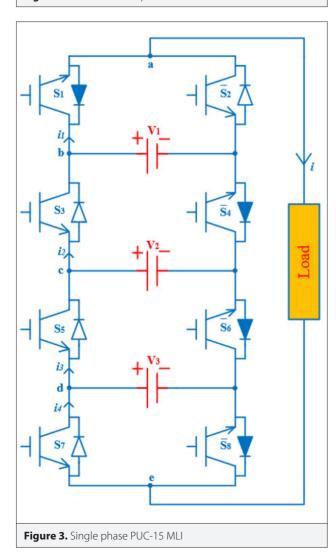

A basic PUC is shown in Figure 2; it consists of 1 voltage source and 2 power switches. This basic PUC generates 3 output voltage levels: +V, 0 and –V. According to the basic PUC structure, 15-level output voltage is developed using three cascaded PUCs. The basic PUC has small power devices for high-quality energy conversions and lower production costs, Figure 3 represents single phase PUC-15 inverter.

Generalized expressions of the number of levels are represented by the equations (1) and (2) [3].

| Table 2.  | <b>Table 2.</b> Modified switching sequence for PUC-15 MLI |                       |                |                       |                                                      |  |  |  |

|-----------|------------------------------------------------------------|-----------------------|----------------|-----------------------|------------------------------------------------------|--|--|--|

| Mode      | <b>S</b> <sub>1</sub>                                      | <b>S</b> <sub>3</sub> | S <sub>5</sub> | <b>S</b> <sub>7</sub> | Level                                                |  |  |  |

| 1         | 1                                                          | 0                     | 0              | 0                     | 7V (V <sub>1</sub> )                                 |  |  |  |

| 2         | 1                                                          | 0                     | 0              | 1                     | 6V (V <sub>1</sub> -V <sub>3</sub> )                 |  |  |  |

| 3         | 1                                                          | 0                     | 1              | 0                     | 5V (V <sub>1</sub> -V <sub>2</sub> +V <sub>3</sub> ) |  |  |  |

| 4         | 1                                                          | 0                     | 1              | 1                     | 4V (V <sub>1</sub> -V <sub>2</sub> )                 |  |  |  |

| 5         | 1                                                          | 1                     | 0              | 0                     | 3V (V <sub>2</sub> )                                 |  |  |  |

| 6         | 1                                                          | 1                     | 0              | 1                     | 2V (V <sub>2</sub> -V <sub>3</sub> )                 |  |  |  |

| 7         | 1                                                          | 1                     | 1              | 0                     | 1V (V <sub>3</sub> )                                 |  |  |  |

| 8         | 0                                                          | 0                     | 0              | 0                     | OV                                                   |  |  |  |

| 9         | 0                                                          | 0                     | 0              | 1                     | -1V (-V <sub>3</sub> )                               |  |  |  |

| 10        | 0                                                          | 0                     | 1              | 0                     | -2V (V <sub>3</sub> -V <sub>2</sub> )                |  |  |  |

| 11        | 0                                                          | 0                     | 1              | 1                     | -3V (-V <sub>2</sub> )                               |  |  |  |

| 12        | 0                                                          | 1                     | 0              | 0                     | -4V (V <sub>2</sub> -V <sub>1</sub> )                |  |  |  |

| 13        | 0                                                          | 1                     | 0              | 1                     | $-5V(V_2-(V_1+V_3))$                                 |  |  |  |

| 14        | 0                                                          | 1                     | 1              | 0                     | -6V (V <sub>3</sub> -V <sub>1</sub> )                |  |  |  |

| 15        | 0                                                          | 1                     | 1              | 1                     | -7V (-V <sub>1</sub> )                               |  |  |  |

| PUC-15: n | PLIC-15: nacked LLcell 15 level: MLI: multilevel inverter  |                       |                |                       |                                                      |  |  |  |

PUC-15: packed U cell 15 level; MLI: multilevel inverter

N (number of organized levels) =  $2^{n+1}$  1 (where n = 1, 2, 3....)

The number of switches required,  $N_{SW}$  depend on the quantity of generation voltage levels N. A generalized expression of  $N_{SW}$  is given by following equation:

$$N = 2^{\frac{Nsw}{2}} - 1$$

The modified switching sequence of PUC-15 MLI is shown in Table 2. This table represents 8 switches  $(S_1 \text{ to } S_8)$  only at the 15 level; and these switches  $(S_1 \text{ and } S_2)$ ,  $(S_3 \text{ and } S_4)$ ,  $(S_5 \text{ and } S_6)$  and  $(S_7 \text{ and } S_8)$  act in a complimentary manner; this means that they operate in opposition, at different time periods, and independently. The modified switching sequence of the 15-level PUC MLI operates mainly 15 operating voltage level modes; for a positive half-cycle, the voltage levels are 7V  $(V_1)$ , 6V  $(V_1-V_2)$ , 5V  $(V_1-V_2+V_3)$ , 4V  $(V_1-V_2)$ , 3V  $(V_2)$ , 2V  $(V_2-V_3)$ , 1V  $(V_3)$ , 0V, -1V  $(-V_3)$ , -2V  $(V_3-V_2)$ , -3V  $(-V_2)$ , -4V  $(V_2-V_1)$ , -5V  $(V_2-(V_1+V_3))$ , -6V  $(V_3-V_1)$ , -7V  $(-V_1)$ . Central mode, which considers all ones or zeros and DC source voltage levels balanced equations, is accomplished by

$$\frac{V_1}{V_2} = \frac{7}{3}$$

,  $\frac{V_2}{V_3} = 3$

$V_1 = 230 \, V_1 V_2 = 99 \, V_2 V_3 = 33 \, V$  are the voltages.

Table 3 represents the conventional switching sequence of a 15-level PUC MLI [6, 7, 17]. Tables 2 and 3 show that for, the switching sequences are quite different; the voltage combinations of modes ((2-3) and (13-14)) are also different, with different switching sequences for particular levels. Moreover, mode 8 is the complete opposite of the conventional switching sequence.

From Figure 3, the node voltage equation is [3, 6, 10, and 11]

**Table 3.** Conventional switching sequence for PUC-15 MLI

| Level &<br>Mode | <b>S</b> <sub>1</sub> | <b>S</b> <sub>3</sub> | S <sub>5</sub> | <b>S</b> <sub>7</sub> | DC voltage combination                                  |

|-----------------|-----------------------|-----------------------|----------------|-----------------------|---------------------------------------------------------|

| 1               | 1                     | 0                     | 0              | 0                     | 7V (V <sub>1</sub> )                                    |

| 2               | 1                     | 0                     | 1              | 0                     | 6V (V <sub>1</sub> -V <sub>2</sub> +V <sub>3</sub> )    |

| 3               | 1                     | 0                     | 0              | 1                     | 5V (V <sub>1</sub> -V <sub>3</sub> )                    |

| 4               | 1                     | 0                     | 1              | 1                     | 4V (V <sub>1</sub> -V <sub>2</sub> )                    |

| 5               | 1                     | 1                     | 0              | 0                     | 3V (V <sub>2</sub> )                                    |

| 6               | 1                     | 1                     | 0              | 1                     | 2V(V <sub>2</sub> -V <sub>3</sub> )                     |

| 7               | 1                     | 1                     | 1              | 0                     | 1V (V <sub>3</sub> )                                    |

| 8               | 1                     | 1                     | 1              | 1                     | OV                                                      |

| 9               | 0                     | 0                     | 0              | 1                     | -1V (-V <sub>3</sub> )                                  |

| 10              | 0                     | 0                     | 1              | 0                     | -2V (V <sub>3</sub> -V <sub>2</sub> )                   |

| 11              | 0                     | 0                     | 1              | 1                     | -3V (-V <sub>2</sub> )                                  |

| 12              | 0                     | 1                     | 0              | 0                     | -4V (V <sub>2</sub> -V <sub>1</sub> )                   |

| 13              | 0                     | 1                     | 1              | 0                     | -5V (V <sub>3</sub> -V <sub>1</sub> )                   |

| 14              | 0                     | 1                     | 0              | 1                     | -6V (V <sub>2</sub> -(V <sub>3</sub> +V <sub>1</sub> )) |

| 15              | 0                     | 1                     | 1              | 1                     | -7V (-V <sub>1</sub> )                                  |

|                 |                       |                       |                |                       |                                                         |

$$V_{ae} = V_{ab} + V_{bc} + V_{cd} + V_{de}$$

Equation (4) represents four node voltages (a, b, c, d) each, and every node voltage is as concise as follows:

$$\begin{cases} V_{ab} = (S_1 - 1)V_1 \\ V_{bc} = (1 - S_3)(V_1 - V_2) \\ V_{cd} = (1 - S_5)(V_2 - V_3) \\ V_{de} = (1 - S_7)V_3 \end{cases}$$

Using eq. (5) in eq. (4),

$$\begin{aligned} &V_{ae} = (S_1 - 1)V_1 + (1 - S_3)(V_1 - V_2) + (V_2 - V_3)(1 - S_5) + (1 - S_7)V_3 \\ &V_{ae} = S_1V_1 - V_1 + V_1 - V_2 - S_3V_1 + S_3V_2 + V_2 - V_3 - S_5V_2 + S_5V_3 + V_3 - S_7V_3 \end{aligned}$$

$$&V_{ae} = (S_1 - S_3)V_1 + (S_3 - S_5)V_2 + (S_5 - S_7)V_3$$

From Figure 3, the current equations at the node b, c, and d are:

$$\begin{cases} \mathbf{i}_1 = \mathbf{S}_1 \mathbf{i}_1 \\ i_2 = S_3 i_l \\ i_3 = S_5 i_l \\ i_4 = S_7 i_l \end{cases}$$

7

Applying Kirchhoff's current law at node b, we obtain the following:

$$\begin{aligned} i_1 &= i_2 + i_{c1} + i_l \\ i_{c1} &= i_1 - i_2 - i_l \\ \frac{dV_1}{dt} &= \frac{(S_1 - S_3)}{C} i_l = \frac{i_l}{c} S_1 - \frac{i_l}{c} S_3 \end{aligned}$$

Applying Kirchhoff's voltage law at node c, we get:

$$i_{2} = i_{3} + i_{c2} + i_{l}$$

$$i_{c2} = i_{2} - i_{3} - i_{l}$$

$$\frac{dV_{2}}{dt} = \frac{(S_{3} - S_{5})}{C} i_{l} = \frac{i_{l}}{c} S_{3} - \frac{i_{l}}{c} S_{5}$$

9

Applying KCL at node d, we obtain:

$$\begin{array}{l} i_3 = i_4 + i_{c3} + i_l \\ i_{c3} = i_3 - i_4 - i_l \\ \frac{dV_3}{dt} = \frac{(S_5 - S_7)}{C} i_l = \frac{i_l}{c} S_5 - \frac{i_l}{c} S_7 \\ \text{Applying KVL at load, we get:} \end{array}$$

11

$$V_l = V_{ae} - i_l R_l - L_l \frac{di_l}{dt}$$

Equation (9) can be rewritten as follows:

$$\frac{di_{l}}{dt} = -\frac{V_{l}}{L_{l}} + \frac{V_{ae}}{L_{l}} - \frac{i_{l}R_{l}}{L_{l}}$$

$$\frac{di_{l}}{dt} = \frac{(S_{1} - S_{3})}{L_{l}}V_{1} + \frac{(S_{3} - S_{5})}{L_{l}}V_{2} + \frac{(S_{5} - S_{7})}{L_{l}}V_{3} - \frac{V_{l}}{L_{l}} - \frac{i_{l}R_{l}}{L_{l}}$$

$$\frac{di_{l}}{dt} = \frac{S_{1}V_{1}}{L_{l}} - \frac{S_{3}V_{1}}{L_{l}} + \frac{S_{3}V_{2}}{L_{l}} - \frac{S_{5}V_{3}}{L_{l}} - \frac{S_{7}V_{3}}{L_{l}} - \frac{V_{l}}{L_{l}} - \frac{i_{l}R_{l}}{L_{l}}$$

12

$$\frac{di_l}{dt} = \frac{S_1 V_1}{L_l} + \frac{(V_2 - V_1)}{L_l} S_3 + \frac{(V_3 - V_2)}{L_l} S_5 - \frac{S_7 V_3}{L_l} - \frac{V_l}{L_l} - \frac{i_l R_l}{L_l}$$

According to models of the state space equation for non-linear systems according to time, varying PUC-15 MLI results in the following:

$$\dot{X} = A(x,t) \times x + B(x,t) \times u + c(t)$$

From equation (11), if the parameters for 15-level PUC MLI  $(X_1=i_1,V_1=X_2,V_2=X_3,V_3=X_4)$  are assumed then the state space equations [3, 6, 10, 11] can be modeled as follows:

$$\begin{split} A(x,t) &= \begin{bmatrix} -R_l \\ L_l \\ 0 \end{bmatrix}, c(t) = \begin{bmatrix} -V_1 \\ L_l \\ 0 \end{bmatrix}, u = \begin{bmatrix} u_1 \\ u_2 \\ u_3 \\ u_4 \end{bmatrix} \\ B(x,t) &= \begin{bmatrix} X_2 \\ L_l \\ 0 \end{bmatrix}, \frac{X_3 - X_2}{L_l} \frac{X_4 - X_3}{L_l} - \frac{X_4}{L_l} \\ \frac{X_1}{L_l} - \frac{X_1}{L_l} \frac{X_1}{L_l} \end{bmatrix} \end{split}$$

### Pulse Width Modification Techniques

Multilevel inverters are usually controlled using various openand closed-loop methods and algorithms [16]. In open-loop methods, PUC-15 MLI topology is controlled with different advanced triangular carrier-based SPWM techniques. The usage methods of carrier-based advanced SPWM techniques are described below.

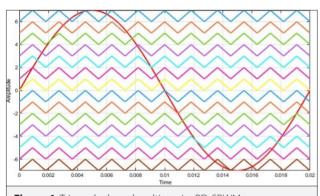

The PUC-15 MLI considers 14 triangular multi-carrier only (number of carriers = number of levels - 1) shown in eq. (15); every triangular carrier has one maximum position at the midpoint of the carrier and two minimum positions at the start and stop positions of the carrier.

$$N_C = N_L - 1$$

where  $N_c$  = number of usage carriers and  $N_L$  = Number of output levels

# Phase Disposition Triangular Based Multi-Carrier Sinusoidal Pulse Width Modulation Technique (PD-SPWM)

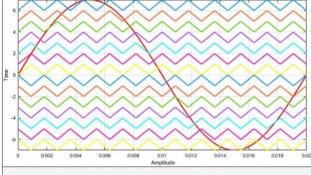

In PD-SPWM method, all 14 carriers are identical and operate on the same switching frequency, with the same amplitude and phase with equal displacements, as shown in Figure 4.

# Phase Opposition Disposition Triangular based Multi-Carrier SPWM Technique (POD-SPWM)

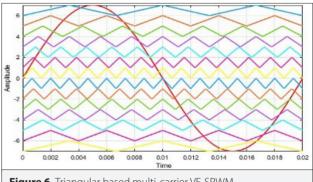

In POD-SPWM method, all 14 carriers are not identical and operate on the same switching frequency with the same amplitude; positive and negative level amplitude carriers are placed with a phase shift between them, as shown in Figure 5.

# Variable Frequency Triangular Carrier-based PWM Technique (VF-SPWM)

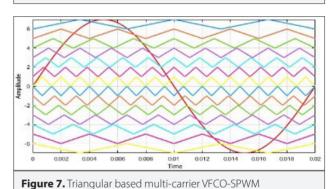

In VF-SPWM method, all 14 carriers are arranged along similar amplitudes and phases but the carriers developed vary for different frequencies, as shown in Figure 6.

# VFCO Variable Frequency Triangular Carrier-based PWM Technique (VF-SPWM)

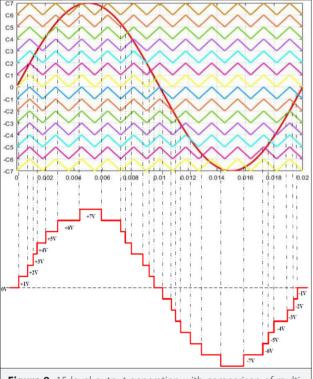

In the VFCO-SPWM method, all 14 carriers are arranged along the same amplitude, negative amplitude level carriers are phase to positive amplitude carriers, and carriers for different frequencies vary, as shown in Figure 7.

### **Analysis of Simulation and Theoretical Results**

The simulations of PUC-15 MLI were carried out using triangular carrier-based advanced SPWM techniques with constant and variable frequencies (PD, phase opposition disposition

Figure 4. Triangular based multi-carrier PD-SPWM

Figure 5. Triangular based multi-carrier POD-SPWM

(POD), VF, and VFCO). Table 4 shows the electrical parameters, Figure 8 shows the simulation model of PUC-15 MLI, and Figure 9 represents the triangular multi-carrier sinewave with 15-level output voltage. PUC-15 level compared sinewave and triangular carriers using a modified switching sequence, with dotted lines representing particular stepwise voltage level indications.

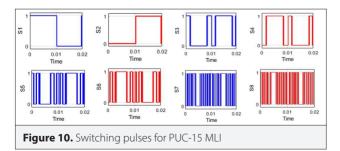

Figure 10 represents the required switching pulses for PUC-15 MLI. These pulses are highly impactful to develop perfect PUC-

Figure 6. Triangular based multi-carrier VF-SPWM

Discrete 5e-05 s.

Figure 8. Simulation model of PUC-15 MLI

Table 4. Load parameters for PUC-15 MLI topology

|                          | . = -                                                             |

|--------------------------|-------------------------------------------------------------------|

| Parameters               | Specifications                                                    |

| DC source voltage (V_dc) | V <sub>1</sub> =230 V, V <sub>2</sub> =99 V, V <sub>3</sub> =33 V |

| Fundamental frequency    | 50 Hz                                                             |

| Switching frequency      | 3 kHz                                                             |

| Load resistance          | 40 Ω                                                              |

| Load inductance          | 3 mH                                                              |

|                          |                                                                   |

PUC-15: packed U cell 15 level; MLI: multilevel inverter

Figure 9. 15 level output generation with comparison of multicarrier & sinewave for PUC MLI

15 level output voltages using modified switching sequences and PWM techniques. The switches  $S_{1}$ ,  $S_{2}$ ,  $S_{3}$ ,  $S_{5}$ , (blue) pulse are normal and operate at different time periods; and the switches  $S_{\gamma}$ ,  $S_{\alpha}$ ,  $S_{\beta}$  (red) pulses are complementary to switches  $S_{\gamma}$ ,  $S_{\gamma}$ ,  $S_{\gamma}$  $S_7$  of PUC-15.

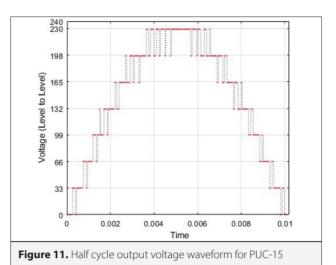

Figure 11 exhibits only positive half-cycle output waveform of PUC-15. This waveform is helpful to find RMS voltage in a graphical analysis because MLIs are non-sinusoidal outputs.

Half-cycle for PUC-15 - seven voltage levels randomly rise, and seven voltage levels fall with same voltage increments and decrements at different time periods.

Peak voltage( $V_0$ )= 230 (V), for 15-level voltages (7 steps up and

$$V_{1p} = \frac{V}{7} = \frac{230}{7} = 32.85 \cong 33$$

(every step needs an increment of 33 volts)

Root mean square voltage for PUC can be calculated by using graphical analysis because MLIs are non-sinusoidal outputs.

$$V_{RMS} = \sqrt{\frac{(Sum \& square \ of \ voltage \ subordinates)}{(Number \ of \ voltage \ subordinates)}}$$

$$= \sqrt{\frac{(V_1^2 + V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2 + V_7^2 + V_8^2 + V_9^2 + V_{10}^2 + V_{11}^2 + V_{12}^2 + V_{13}^2 + V_{14}^2 + V_0^2)}{(15)}}$$

$$= \sqrt{\frac{(33^2 + 66^2 + 99^2 + 132^2 + 165^2 + 198^2 + 230^2 + 230^2 + 198^2 + 165^2 + 132^2 + 99^2 + 66^2 + 33^2 + 0^2)}{(15)}}$$

One half-cycle contain 15 time periods  $T_p = 10 \, ms \, (T = 0.01)$

One pulse width time period  $T_{1p} = \frac{T}{15} = 0.0006666$  (pulse to pulse 0.0006666 ms)

One half-cycle contain 15 different firing angles  $\theta_{s} = 180^{\circ}$

One firing angle for one pulse width  $\theta_{1a} = \frac{180^{\circ}}{15} = 12^{\circ}$  (every pulse to pulse varies at a 12° firing angle)

Table 5 represents firing angles for every peak voltage. All peak voltages are represented in the middle of the table. At V<sub>n</sub> the voltage is 33V, with a voltage firing angle and decrement firing angle of 12° and 168°, respectively, before and after the time period of 0.005 ms.

**Table 5.** Firing angles for PUC-15 MLI topology at peak voltage

| Voltage<br>increment angle | Peak<br>voltage (Vp) | Voltage<br>decrement angle |

|----------------------------|----------------------|----------------------------|

| 0°                         | 0                    | 180°                       |

| 120                        | 33                   | 168°                       |

| 240                        | 66                   | 156°                       |

| 36°                        | 99                   | 144°                       |

| 480                        | 132                  | 132º                       |

| 60°                        | 165                  | 120°                       |

| 72°                        | 198                  | 108°                       |

| 840                        | 230                  | 96°                        |

PUC-15: packed U cell 15 level; MLI: multilevel inverter

Figure 12. Performances analysis of PUC-15 MLI based on PD-SP-WM

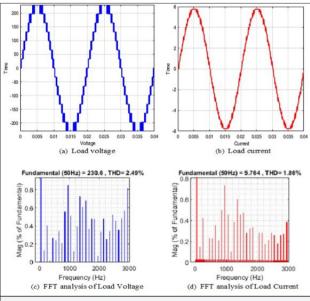

# Phase Disposition Triangular Based Multi-Carrier SPWM Technique (PD-SPWM)

The simulation results in Figure 12 (a-d) represent the load voltage, load current output waveforms, and THD analysis presented at MI 1.0. The THD values of the phase voltage and currents are 2.49% and 1.86%, respectively.

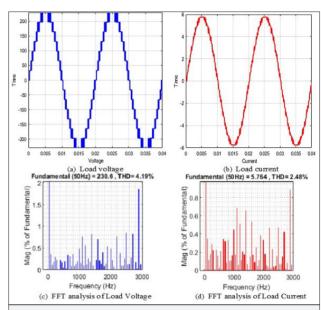

Phase Opposition Disposition Triangular based Multi-Carrier SPWM technique (PS-SPWM

The simulation results in Figure 13 (a-d) represent the load voltage, load current output waveforms, and THD analysis presented at MI 1.0. The THD values of the phase voltage and currents are 4.19% and 2.48%, respectively.

**Figure 13.** Performances analysis of PUC-15 MLI based on POD-SPWM

**Figure 14.** Performances analysis of PUC-15 MLI based on VF-SP-WM

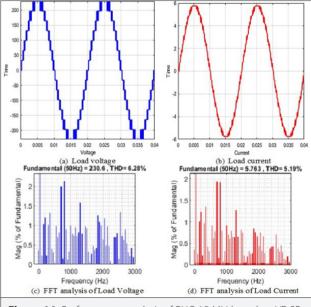

# Variable Frequency Triangular Carrier-based PWM Technique (VF-SPWM)

The simulation results in Figure 14 (a-d) represent the load voltage, load current output waveforms, and THD analysis presented at MI 1.0. The THD values of the phase voltage and currents are 6.28% and 5.19%, respectively.

# Variable Frequency Carrier Opposition Triangular Carrier-based PWM Technique (VFCO-SPWM)

The simulation results in Figure 15 (a-d) represent the load voltage, load current output waveforms, and THD analysis present-

ed at MI 1.0. The THD values of the phase voltage and currents are 5.88% and 4.68%, respectively.

### **Performance Analysis**

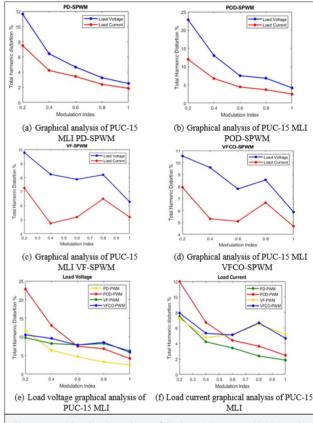

The THD percentage of PUC-15 MLI was analyzed in terms of Fast Fourier Transform analysis using different PWM techniques at modulation index of M = 1, 0.8, 0.6, 0.4, and 0.2. Table 4 compares the THD percentage of PUC-15 for different PWM techniques at M = 1. Tables 6–11 represent the same at M = 0.8, 0.6, 0.4, and 0.2, respectively; and Figures (12-15) represent the THD graph analysis for PD-PWM, POD-PWM, VF-PWM, VFCO-PWM at M = 0.8, 0.6, 0.4, and 0.2, respectively, for load voltage and load currents.

The modulation index is defined by  $M = \frac{A_r}{A_c}$  where  $A_r =$  reference signals for amplitude and  $A_c =$  carrier signals for amplitude.

**Figure 15.** Performances analysis of PUC-15 MLI based on VF-CO-SPWM

**Table 6.** Comparison of THD percentages of PUC-15 for different PWM techniques at M=1

|              | Triangular PWM |           |                    |      |  |  |  |

|--------------|----------------|-----------|--------------------|------|--|--|--|

|              | Constant       | frequency | Variable frequency |      |  |  |  |

| THD          | PD             | POD       | VF                 | VFCO |  |  |  |

| Load voltage | 2.49           | 4.19      | 6.28               | 5.88 |  |  |  |

| Load current | 1.86           | 2.48      | 5.19               | 4.68 |  |  |  |

PUC-15: packed U cell 15 level; THD: total harmonic distortion; PWM: pulse width modulation; PD: phase disposition; POD: phase opposition disposition; VF: variable frequency; VFCO: variable frequency carrier opposition

The overall performances of PWM techniques were analyzed for constant and variable frequencies using Tables 6-11 and Figures 16 (a-f). It is evident that at a constant frequency, the PD-SPWM technique has a THD of 2.49% and 1.86% at M = 1; 3.26% and 2.38% at M = 0.8; 4.66% and 3.42% at M = 0.6; 6.41% and 4.21% at M = 0.4; 11.63% and 7.48% at M = 0.2, respectively, for load voltage and load currents. The POD-SPWM technique has a THD of 4.19% and 2.48% at M = 1; 6.80% and 3.65% at M = 0.8; 7.50% and 4.40% at M = 0.6; 13.04% and 6.71% at M = 0.4; 22.86% and 11.98% at M = 0.2, respectively, for load voltage and load currents. At VF, the VF-SP-WM technique has a THD of 6.28% and 5.19% at M = 1; 8.20% and

**Table 7.** Comparison of THD percentage of PUC-15 for different PWM techniques at M = 0.8

|              | Triangular PWM |           |          |           |  |  |  |

|--------------|----------------|-----------|----------|-----------|--|--|--|

|              | Constant       | frequency | Variable | frequency |  |  |  |

| THD          | PD             | POD       | VF       | VFCO      |  |  |  |

| Load voltage | 3.26           | 6.80      | 8.20     | 8.55      |  |  |  |

| Load current | 2.38           | 3.65      | 6.48     | 6.66      |  |  |  |

THD: total harmonic distortion; PWM: pulse width modulation; PD: phase disposition; POD: phase opposition disposition; VF: variable frequency; VFCO: variable frequency carrier opposition

**Table 8.** Comparison of THD percentage of PUC-15 for different PWM Techniques at M=0.6

|              | Triangular PWM |           |                    |      |  |  |  |

|--------------|----------------|-----------|--------------------|------|--|--|--|

|              | Constant       | frequency | Variable frequency |      |  |  |  |

| THD          | PD             | POD       | VF                 | VFCO |  |  |  |

| Load voltage | 4.66           | 7.50      | 7.87               | 7.80 |  |  |  |

| Load current | 3.42           | 4.40      | 5.18               | 5.09 |  |  |  |

|              |                |           |                    |      |  |  |  |

THD: total harmonic distortion; PWM: pulse width modulation; PD: phase disposition; POD: phase opposition disposition; VF: variable frequency; VFCO: variable frequency carrier opposition

**Table 9.** Comparison of THD percentage of PUC-15 for different PWM Techniques at M = 0.4

|              | Triangular PWM |           |                    |      |  |  |  |

|--------------|----------------|-----------|--------------------|------|--|--|--|

|              | Constant       | frequency | Variable frequency |      |  |  |  |

| THD          | PD             | PD POD    |                    | VFCO |  |  |  |

| Load voltage | 6.41           | 13.04     | 8.23               | 9.58 |  |  |  |

| Load current | 4.21           | 6.71      | 4.74               | 5.31 |  |  |  |

THD: total harmonic distortion; PWM: pulse width modulation; PD: phase disposition; POD: phase opposition disposition; VF: variable frequency; VFCO: variable frequency carrier opposition

6.48% at M = 0.8; 7.87% and 5.18% at M = 0.6; 8.23% and 4.74% at M = 0.4; 9.78% and 7.26% at M = 0.2, respectively, for load voltage and load currents. The VFCO-SPWM technique has low THD values of 5.88% and 4.68% at M = 1; 8.55% and 6.66% at M = 0.8; 7.80% and 5.09% at M = 0.6; 9.58% and 5.31% at M = 0.4; 10.56% and 7.93% at M = 0.2, respectively, for load voltage and load current, as shown in Table 9. These are also evident axiomatically when the modulation index M is increased. The THD percentage is reduced randomly in constant frequency SPWM methods, and PD-SPWM technique has lower THD percentage at M = 1, thereby proving that the modified switching sequence also works perfectly for the respective PWM techniques.

### **Conclusion**

In this study, the performance of PUC-15 MLI with modified switching sequence was analyzed using numerical analyses and simulations. The proposed switching sequence has benefits including an improved harmonic spectrum, optimized switching sequence obtained by controlling the burden on the switch, and controlled switching frequency compared with other conventional multilevel inverters. The simulated results are compared with advanced triangular carrier-based PWM

**Table 10.** Comparison of THD percentage of PUC-15 for different PWM Techniques at M=0.2

|              | Triangular PWM |           |                    |       |  |  |  |

|--------------|----------------|-----------|--------------------|-------|--|--|--|

|              | Constant       | frequency | Variable frequency |       |  |  |  |

| THD          | PD             | POD       | VF                 | VFCO  |  |  |  |

| Load voltage | 11.63          | 22.86     | 9.78               | 10.56 |  |  |  |

| Load current | 7.48           | 11.98     | 7.26               | 7.93  |  |  |  |

THD: total harmonic distortion; PWM: pulse width modulation; PD: phase disposition; POD: phase opposition disposition; VF: variable frequency; VFCO: variable frequency carrier opposition

techniques with constant frequencies (PD, POD) and variable frequencies (VF, VFCO) at different modulation indices of M = 0.2, 0.4, 0.6, 0.8, and 1. The advanced carrier-based PD modulation technique produces better results than the POD, VF, and VFCO-PWM techniques in terms of %THD—the voltage and current THDs are 2.49% and 1.86% at M = 1, and these come under the IEEE-519 standard.

**Figure 16.** Graphical analysis of PUC-15 MLI using SPWM techniques

**Table 11.** Comparison of THD percentage of PUC-15 for different PWM Techniques at M = (1.0 to 0.2)

|     |                           |                    |              | Triangu      | lar PWM                   |                    |                          |      |  |

|-----|---------------------------|--------------------|--------------|--------------|---------------------------|--------------------|--------------------------|------|--|

|     |                           | Constant frequency |              |              |                           | Variable frequency |                          |      |  |

|     | PD                        |                    | POD          |              | VF                        |                    | VFCO                     |      |  |

| MI  | Load voltage Load current |                    | Load voltage | Load current | Load voltage Load current |                    | Load voltage Load curren |      |  |

| 1.0 | 2.49                      | 1.86               | 4.19         | 2.48         | 6.28                      | 5.19               | 5.88                     | 4.68 |  |

| 0.8 | 3.26                      | 2.38               | 6.80         | 3.65         | 8.20                      | 6.48               | 8.55                     | 6.66 |  |

| 0.6 | 4.66                      | 3.42               | 7.50         | 4.40         | 7.87                      | 5.18               | 7.80                     | 5.09 |  |

| 0.4 | 6.41                      | 4.21               | 13.04        | 6.71         | 8.23                      | 4.74               | 9.58                     | 5.31 |  |

| 0.2 | 11.63                     | 7.48               | 22.86        | 11.98        | 9.78                      | 7.26               | 10.56                    | 7.93 |  |

MI: modulation index; PWM: pulse width modulation; PD: phase disposition; POD: phase opposition disposition; VF: variable frequency; VFCO: variable frequency carrier opposition

**Peer-review:** Externally peer-reviewed.

**Author Contributions:** Concept - N.K.M.; Design – N.K.M.; Supervision – S.M.; Data Collection and/or Processing – N.K.M.; Analysis and/or Interpretation – N.K.M.; Literature Search – N.K.M.; Writing Manuscript – N.K.M.

**Conflict of Interest:** The authors have no conflicts of interest to declare

**Financial Disclosure:** The authors declared that this study has received no financial support.

#### References

- L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, M.A.M. Prats, "The age of multilevel converters arrives", IEEE Industrial Electronics Magazine, vol. 2, no. 2, pp.28-39, Jan 2008. [Crossref]

- M. Vijeh, M. Rezanejad, E. Samadaei, K. Bertilsson, "A General Review of Multilevel Inverters Based on Main Submodules: Structural Point of View" in IEEE Transactions on Power Electronics, vol. 34, no. 10, pp. 9479-9502, Oct. 2019. [Crossref]

- A. Nabae, I. Takahashi, H. Akagi, "A New Neutral-Point-Clamped PWM Inverter," in IEEE Transactions on Industry Applications, vol. IA-17, no. 5, pp. 518-523, Sept. 1981. [Crossref]

- T. Meynard, A.M. Lienhardt, G. Gateau, Ch. Haederli, P. Barbosa, "Flying capacitor multilevel converters with reduced stored energy" IEEE ISIE July 2006. https://ieeexplore.ieee.org/document/4078207. [Crossref]

- M. Malinowski, K. Gopakkumar, J. Rodriguez, M.A. Perez, "A survey on cascaded multilevel inverters", IEEE Trans. industrial Electron., vol. 57, no. 7, pp. 2197-2206, July, 2010. [Crossref]

- Y. Ounejjar, K. Al-Haddad, L. Gregoire, "Packed U Cells Multilevel Converter Topology: Theoretical Study and Experimental Validation," in IEEE Transactions on Industrial Electronics, vol. 58, no. 4, pp. 1294-1306, April 2011. [Crossref]

- N.R. Patnaik, Y.R. Tagore, "Design and evaluation of PUC (Packed U Cell) topology at different levels and loads in terms of THD", European Journal of Advances in Engineering and Technology, vol. 3, no. 9, pp.33-43, Sep 2016.

- Y. Ounejjar, K. Al-Haddad, "Fourteen-band hysteresis controller of the fifteen-level packed U cells converter," IECON 2010 - 36th Annual Conference on IEEE Industrial Electronics Society, Glendale, AZ, pp. 475-480, 2010. [Crossref]

- S. Arazm, I. Kamwa, K. Al-Haddad, "Model Predictive Control on Grid Connected FifteenLevel Packed U-Cell (PUC15) Inverter", 2019 IEEE elecctrical power & energy conferense. [Crossref]

- R.P. Narasipuram, "Optimal design and analysis of hybrid photovoltaic-fuel cell power generation system for an advanced con-

- verter technologies", Int. J. Mathematical Modelling and Numerical Optimisation, vol. 8, no. 3, pp.245-276, Jan 2018. [Crossref]

- N. Rajanand Patnaik, Y. R. Tagore, S. Chaitanya, "Advanced seven level transformer-less multilevel inverter topology for PV application," 2017 Third International Conference on Advances in Electrical, Electronics, Information, Communication and Bio-Informatics (AEEICB), Chennai, pp. 111-116, 2017. [Crossref]

- R.P. Narasipuram, R.T. Yadlapalli, R.T. "Performance analysis and design optimisation of 3-Ø Packed U Cell inverter for industrial drive applications", Int. J. Mathematical Modelling and Numerical Optimisation, vol. 9, no. 3, pp. 309-337, Jan 2019. [Crossref]

- E. Samadaei, A. Sheikholeslami, S. Gholamian, J. Adabi, "A square T-type (ST-type) module for asymmetrical multilevel inverters", IEEE Trans. Power Electron., vol. 33, no. 2, pp. 987-996, Feb. 2018. [Crossref]

- E. C. d. Santos, J. H. G. Muniz, E. R. C. da Silva, C. B. Jacobina, "Nested Multilevel Topologies," in IEEE Transactions on Power Electronics, vol. 30, no. 8, pp. 4058-4068, Aug. 2015. [Crossref]

- S. T. Meraj, K. Hasan, A. Masaoud, "A Modified Configuration of Cross-Switched T-Type (CT-Type) Multilevel Inverter," in IEEE Transactions on Power Electronics, vol. 35, no. 4, pp. 3688-3696, April 2020. [Crossref]

- M. Tariq, M. Meraj, A. Azeem, A. I. Maswood, A. Iqbal, B. Chokkalingam, "Evaluation of level-shifted and phase-shifted PWM schemes for seven level single-phase packed U cell inverter," in CPSS Transactions on Power Electronics and Applications, vol. 3, no. 3, pp. 232-242, Sept. 2018. [Crossref]

- A. Azeem, M.K. Ansari, M. Tariq, A. Sarwar, I. Ashraf, "Design and Modeling of Solar Photovoltaic System Using Seven-Level Packed U-Cell (PUC) Multilevel Inverter and Zeta Converter for Off-Grid Application in India", Electrica vol. 19, no. 2, pp. 101-112, Dec 2019. [Crossref]

- K. Karaarslan, B. Arifoğlu, E. Beşer, S. Çamur, "Single phase series active power filter based on 15-level cascaded inverter topology," 2017 4th International Conference on Electrical and Electronic Engineering (ICEEE), Ankara, pp. 37-42, 2017. [Crossref]

- T. Balasudha, M. Logeswari, A. Nandini, S. Maheswari, "Design and Implementation of a 15-Level Inverter with Facts Capability for Distributed Energy Systems" International Conference on Systems, Science, Control, Communication, Engineering and Technology 2016 [ICSSCCET 2016], pp. 227-230.

- Z. Salam, A. Majed, A.M. Amjad, "Design and implementation of 15-level cascaded multi-level voltage source inverter with harmonics elimination pulse-width modulation using differential evolution method." IET Power Electronics, vol. 8, no. 9, pp. 1740-1748, Sep 2015. [Crossref]

- J.G. Shankar, J.B. Edward, "Design and Implementation of 15-Level Asymmetric Cascaded H Bridge Multilevel Inverter," Journal of Electrical Engineering, vol. 17, no. 2, pp. 396-404, Jun 2017.

# Electrica 2021; 21(2): 272-282 Kumar Muthukuri and Mopidevi. Modified Switching for PUC-15 Topology with LS-SPWM Techniques

Narendra Kumar Muthukuri received a Bachelor's degree in Technology from JNTUK in 2014 and Master's degree in Technology from JNTUK in 2016. He worked for 2.5 years (2016–2019) as an assistant professor at the GVR&S College of Engineering and Technology. He is presently a full-time research scholar at the Department of EEE, Vignan's Foundation for Science, Technology, and Research, Guntur, India. His research interests include power electronic converters, grid connected and stand-alone applications, and EV applications.

Mopidevi Subbarao received his Bachelor's degree in Technology from JNTUH in 2004, Master's degree in Technology from JNTUA in 2007, and PhD from JNTUK in 2019. He is presently working in the Department of EEE, Vignan's Foundation for Science, Technology, and Research, Guntur, India. His research interests include EV battery chargers, microgrids, PFC converters, and fuzzy intelligent systems.